Computer Buses

740 likes | 1.49k Vues

Computer Buses. SJSU - Fall 2008 CS 147 Vu Luu. Contents. 1. Concepts 2. Measurement 3. Operation. Concepts. A bus is a collection of wires and connectors through which the data is transmitted. Bus = address bus + data bus Data bus: transfers actual data.

Computer Buses

E N D

Presentation Transcript

Computer Buses SJSU - Fall 2008 CS 147 Vu Luu

Contents 1. Concepts 2. Measurement 3. Operation

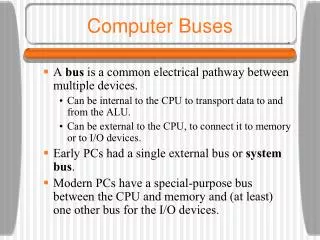

Concepts • A bus is a collection of wires and connectors through which the data is transmitted. • Bus = address bus + data bus • Data bus: transfers actual data. • Address bus: transfers information about data and where it should go.

Concepts (cont.) • Bus protocol: rules determining the format and transmission of data through bus. • Parallel bus: data is transmitted in parallel. • Advantage: fast • Disadvantage: high cost for long distance transmission, interference between lines at high frequency. • Serial bus: data is transmitted in serial. • Advantage: low cost for long distance transmission, no interference. • Disadvantage: slow • Bus master: The device controls bus. Other devices are slaves.

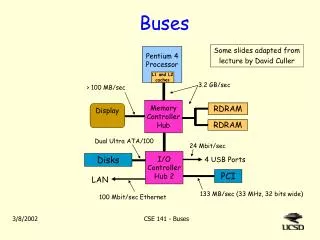

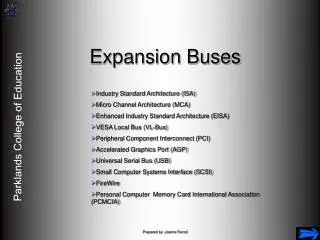

Concepts (cont.) • Local (system) bus: CPU main memory. • Front side bus: • Original concept: CPU components • Modern Intel architecture: CPU NorthBridge chipset • Back side bus: CPU L2 cache • Memory bus: Northbridge chipset main memory • AGP bus: Northbridge chipset GPU • ISA, EISA, VLB, PCI, Firewire, USB, PCI-Express bus: motherboard peripheral devices.

Measurement • Bus width: indicates the number of wires in the bus for transferring data. • Bus bandwidth: refers to the total amount of data that can theoretically be transferred on the bus in a given unit of time.

Synchronous Bus vs. Asynchronouse Bus • A bus can be classified as one of two type: synchronous and asynchronous. • Synchronous bus: there is a common clock that synchronizes bus operations. • Asynchronous bus: there is no common clock. Bus master and slaves have to “handshake” during transmission process.

1. CPU places address of the location it wants to read on the address lines. 1

2. After the voltages on the address lines have become stable, CPU asserts MREQ and RD lines. 1 2

3. Memory controller locates memory location and loads it into data lines. 1 3 2

4. CPU takes data from data lines and then de-asserts MREQ and RD to release the bus. 1 3 2 4

1 1. CPU puts address on the bus.

1 2. CPU asserts MREQ and RD lines. 2

1 3. CPU asserts MSYN line. Memory controller locates and loads data from memory to data lines. 2 3

1 4. Memory controller locates, loads data from memory to data lines, and asserts SSYN line. 2 3 4 4

1 5. CPU takes data from data lines and then de-asserts MREQ, RD, and MSYN. 5 2 5 3 5 4 4

1 6. Finally, memory controller de-assert SSYN. 5 2 5 3 5 4 4 6

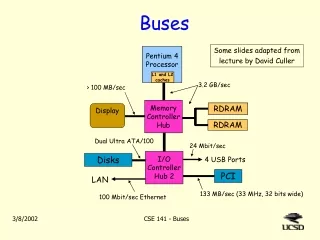

Bridge-based bus architectures • System includes a lot of buses which are segregated by bridges. • Advantage: buses can simultaneously operate. • Intel architecture:

Internal Communication Methodologies • Programmed I/O (polling) • Interrupt-drive I/O • Direct Memory Access (DMA)

Programmed I/O (polling) • CPU polls each device to see if it needs servicing. • Drawback: The CPU wastes time for polling devices (busy-wait.)

Interrupt-Drive I/O (PIO) • Device requests service through a special interrupt request line that goes directly to the CPU. • No busy-wait. More efficient than PIO.

Direct Memory Access (DMA) • Devices transfer data directly to and from memory bypasses the CPU. • Very efficient mode. CPU is free to do other operations.

References • Murdocca, Miles and Heuring, Vincent. Computer Architecture and Organization: An Integrated Approach. John Wiley & Sons, Inc., 2007. p.303 – p.316. • Kozierok, Charles. The PC Guide.http://www.pcguide.com/.