做实验过程中发现的问题:

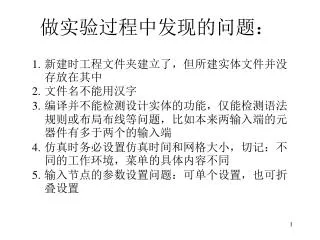

做实验过程中发现的问题:. 新建时工程文件夹建立了,但所建实体文件并没存放在其中 文件名不能用汉字 编译并不能检测设计实体的功能,仅能检测语法规则或布局布线等问题,比如本来两输入端的元器件有多于两个的输入端 仿真时务必设置仿真时间和网格大小,切记:不同的工作环境,菜单的具体内容不同 输入节点的参数设置问题:可单个设置,也可折叠设置. 6. 警告可以忽略,但能解决的尽可能解决;错误必须改正。比如:如果在 settings|files 中添加过某实体文件,但该实体文件名被更改或删除,则可能出现警告,所以,只要将更名前的那个路径删除就可以

做实验过程中发现的问题:

E N D

Presentation Transcript

做实验过程中发现的问题: • 新建时工程文件夹建立了,但所建实体文件并没存放在其中 • 文件名不能用汉字 • 编译并不能检测设计实体的功能,仅能检测语法规则或布局布线等问题,比如本来两输入端的元器件有多于两个的输入端 • 仿真时务必设置仿真时间和网格大小,切记:不同的工作环境,菜单的具体内容不同 • 输入节点的参数设置问题:可单个设置,也可折叠设置

6. 警告可以忽略,但能解决的尽可能解决;错误必须改正。比如:如果在settings|files中添加过某实体文件,但该实体文件名被更改或删除,则可能出现警告,所以,只要将更名前的那个路径删除就可以 7. 提示硬件问题时,可尝试插紧并行口和JTAG口的插头 8. 下载后实验箱没反应时,要考虑引脚锁定后是否再次编译了 • 下载编程方式只需首次下载时设定,不必每次去设;下载时,要选中“program/configue”,其余可不选 • 提示工程不能打开时,将所在工程文件夹的只读属性去掉即可

第3章VHDL •本章概要:本章介绍硬件描述语言VHDL的语言要素、程序结构以及描述风格,并介绍最基本、最典型的数字逻辑电路的VHDL描述,作为VHDL工程设计的基础。 •知识要点: (1)VHDL设计实体的基本结构。 (2)VHDL的语言要素。 (3)用VHDL实现各种类型电路及系统的方法。 (4)VHDL设计流程。

3.1 VHDL基本知识 VHDL作为IEEE标准的硬件描述语言和EDA的重要组成部分,经过十几年的发展、应用和完善,以其强大的系统描述能力、规范的程序设计结构、灵活的语言表达风格和多层次的仿真测试手段,在电子设计领域受到了普遍的认同和广泛的接受,成为现代EDA领域的首选硬件设计语言。专家认为,在新世纪中,VHDL与Verilog语言将承担起几乎全部的数字系统设计任务。

库、程序包 设 计 实 体 实体(ENTITY) 结构体 (ARCHITECTURE) 进程 或其它并行结构 配置(CONFIGURATION) 3.1.1 VHDL程序设计基本结构

VHDL的 描述风格

VHDL语言的描述风格 一般有四种常用描述风格: • 行为描述:只描述电路的功能或行为,不 包含任何硬件信息等。 • 数据流描述(RTL描述):反映数据经过 一定的逻辑运算后在输入和输 出间的传递。 • 结构描述:以元件或已完成的功能模块为 基础,应用于采用元件例化的 VHDL程序设计中。 • 前三种的综合

【补充例1】2选1多路选择器的行为描述程序。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux21 IS PORT( a,b : IN STD_LOGIC; s: IN STD_LOGIC; y: OUT STD_LOGIC ); END ENTITY mux21; ARCHITECTURE behav OF mux21 IS BEGIN PROCESS(a,b,s) BEGIN IF s='0' THEN y<=a; ELSE y<=b; END IF; END PROCESS; END ARCHITECTURE behav;

【补充例2】2选1多路选择器数据流描述程序。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux21 IS PORT( a,b : IN STD_LOGIC; s: IN STD_LOGIC; y: OUT STD_LOGIC ); END ENTITY mux21; ARCHITECTURE dataflow OF mux21 IS BEGIN y<=(a AND (NOT s)) OR (b AND s); END ARCHITECTURE dataflow;

【补充例3】 2选1多路选择器结构描述程序。LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY and21 IS --与门 PORT(i0,i1 : IN STD_LOGIC; q: OUT STD_LOGIC ); END ENTITY and21; ARCHITECTURE one OF and21 IS BEGIN q<=i0 AND i1; END ARCHITECTURE one; LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY or21 IS --或门 PORT(i0,i1 : IN STD_LOGIC; q: OUT STD_LOGIC ); END ENTITY or21; ARCHITECTURE one OF or21 IS BEGIN q<=i0 OR i1; END ARCHITECTURE one; LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY inv21 IS --非门 PORT(i0 : IN STD_LOGIC; q: OUT STD_LOGIC ); END ENTITY inv21; ARCHITECTURE one OF inv21 IS BEGIN q<= (NOT i0); END ARCHITECTURE one; ] LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux21 IS PORT(a,b : IN STD_LOGIC; s: IN STD_LOGIC; y: OUT STD_LOGIC ); END ENTITY mux21; ARCHITECTURE struct OF mux21 IS COMPONENT and21 PORT (i0,i1 : IN STD_LOGIC; q: OUT STD_LOGIC); END COMPONENT; COMPONENT or21 PORT (i0,i1 : IN STD_LOGIC; q: OUT STD_LOGIC); END COMPONENT; COMPONENT inv21 PORT (i0: IN STD_LOGIC; q: OUT STD_LOGIC); END COMPONENT; SIGNAL tmp1,tmp2,tmp3:STD_LOGIC; BEGIN u1: and21 PORT MAP (b, s,tmp1); u2: inv21 PORT MAP(s,tmp2); u3: and21 PORT MAP (a,tmp2,tmp3); u4: or21 PORT MAP(tmp1,tmp3,y); END ARCHITECTURE struct; ] ]

3.1.1 库、程序包 库(LIBRARY)——存放预先设计好的程序包和数据的集合体。 程序包(PACKAGE)——将已定义的数据类型、元件调用说明及子程序收集在一起,供VHDL设计实体共享和调用,若干个包则形成库。 IEEE库包括:STD_LOGIC_1164 STD_LOGIC_ARITH——是SYNOPSYS公司加入IEEE库程序包,包括: STD_LOGIC_SIGNED(有符号数) STD_LOGIC_UNSIGNED(无符号数)

STD_LOGIC_SMALL_INT(小整型数) VHDL ’87版本使用IEEE STD 1076-1987 语法标准 VHDL ’93版本使用IEEE STD 1076-1993 语法标准 例:LIBRARY IEEE USE IEEE.STD_LOGIC_1164.ALL 描述器件的输入、输出端口数据类型中将要用到的IEEE的标准库中的STD_LOGIC_1164程序包。

3.1.2 实体(ENTITY)说明 格式: ENTITY 实体名 IS [类属参数说明] [端口说明] END 实体名; 规则:(1)类属参数说明必须放在端口说明之前,用于设计实体和外部环境通信的参数,传递静态信息,特别是用来规定一个实体的端口大小、元件的数量、实体的物理特性(如矢量位数、延迟时间)等参数。 (2)类属与常数不同,常数只能从设计实体的内部得到赋值,且不能改变,而类属的值可以由设计实体外部提供。通过修改类属参量,设计可很方便地改变一个设计的内部结构和规模。

例如 : GENERIC(m:TIME:=1 ns); --说明m是一个值为1ns的时间参数 则程序语句: tmp1 <= d0 AND se1 AFTER m; --表示d0 AND se1经1ns延迟后才送到tmp1。

【补充例】 n输入端与非门的实体描述: ENTITY nand_n IS GENERIC ( n : INTEGER ) ; PORT( a : IN STD_LOGIC_VECTOR(n-1 DOWNTO 0); s : OUT STD_LOGIC ); END ENTITY nand_n; 其中,n可以在定义时初始化,也可以在应用时利用类属映射语句来指定,如: nand_n:GENERIC MAP(n>=3);

(2)端口说明是描述器件的外部接口信号的说明,相当于器件的引脚说明。其格式为:(2)端口说明是描述器件的外部接口信号的说明,相当于器件的引脚说明。其格式为: PORT(端口名{,端口名}:方向 数据类型名; : 端口名{,端口名}:方向 数据类型名); 例如:PORT(a,b:IN STD_LOGIC; s:IN STD_LOGIC; y:OUT STD_LOGIC);

D Q BUFFER 端口 端口方向包括: IN; --输入, 符号: OUT; --输出, 符号: INOUT;--双向, 符号: BUFFER; --具有读功能的输出,符号为:

out 和buffer 的区别: 总之,只有当端口模式为IN、INOUT和BUFFER时,才能从该端口读数据,只有在端口模式为OUT、INOUT和BUFFER时,才能从该端口写数据。

3.1.3 结构体(ARCHITECTURE) 基本设计单元的实体,用于指明设计基本单元的行为、元件及内部连接关系,即定义设计单元的功能。 结构体的结构: ARCHITECTURE 结构体名 OF 实体名 IS [说明语句]; --为内部信号、常数、数据类型、函数定义 BEGIN [功能描述语句] END ARCHITECTURE 结构体名;

常数说明 结构体说明 数据类型说明 信号说明 结构体 例化元件说明 子程序说明 块语句 结构体功能描述 进程语句 信号赋值语句 子程序调用语句 元件例化语句

实体与结构体的关系: 一个设计实体可有多个结构体,代表实体的多种实现方式。各个结构体的地位相同。 结构体1 结构体2 结构体3 设计实体 . . . 结构体n

例如:或门的结构体 ARCHITECTURE or1 OF temp1 IS SIGNAL y:STD_LOGIC; BEGIN y<=a OR b; END ARCHITECTURE or1; 3.1.4 配置(CONFIGURATION)——把特定的结构体关联(指定给)一个确定的实体,为大型系统的设计提供管理和工程组织。 配置:从某个实体的多种结构体描述方式中选择特定的一个。

3.1.2 基本逻辑器件的描述 【例3.1】或门的描述 LIBRARY IEEE; USE IEEE.STDLOGIC1164.ALL; ENTITY or1 IS PORT( a,b:IN STD_LOGIC; y:OUT STDLOGIC); END or1; ARCHITECTURE example1 OF or1 IS BEGIN y<=a OR b; END example1;

a so b co 【例3.2】半加器的描述 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_adder IS PORT(a,b:IN STD_LOGIC; so,co:OUT STD_LOGIC); END h_adder; ARCHITECTURE example2 OF h_adder IS BEGIN so<=a XOR b; co<=a AND b; END example2;

a y b s 【例3.3】2选1数据选择器的描述 LIBRARY IEEE; USE IEEE.STDLOGIC1164.ALL; ENTITY mux21 IS PORT( a,b:IN STDLOGIC; s:IN STDLOGIC; y:OUT STDLOGIC); END mux21; ARCHITECTURE example3 OF mux21 IS BEGIN y<=a WHEN s=’0’ ELSE b; END ARCHITECTURE example3;

q d D Q ena 【例3.4】锁存器的描述

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY latch1 IS PORT ( d :IN STD_LOGIC; ena :IN STD_LOGIC; q :OUT STD_LOGIC); END latch1; ARCHITECTURE example4 OF latch1 IS SIGNAL sig_save: STD_LOGIC:=‘0’;

BEGIN PROCESS (d,ena) BEGIN IF ena='1' THEN sig_save<=D; END IF; Q<=sig_save; END PROCESS; END example4; 返回

3.2 VHDL语言要素 VHDL具有计算机编程语言的一般特性,其语言要素是编程语句的基本单元。准确无误地理解和掌握VHDL语言要素的基本含义和用法,对正确地完成VHDL程序设计十分重要。

关键字(保留字) 与其他任何计算机语言一样,VHDL语言要求我们遵守定义了关键字(keyword)和语法(syntax)的一整套规则。“关键字”是在语言中具有特别含义的单词,它只能作为固定的用途,用户不能用保留字作为标识符。 如:abs,after,all,and,architecture, array, attribute, begin,body, buffer,case,component, constant, downto,else,elsif,end,entity,exit, file, for,function, generate, group, if,in,is,library,loop,map ,mod, nand,new,next,nor,not,of ,on,open ,or ,others,out,package, process,procedure, range,record, rem, report, rol, ror, select, shared, signal,sla,sll,sra,subtype, then,to,type,use,until, variable,wait, when,while,with,xor,xnor等。

3.2.1 VHDL文字规则 1. 数字型文字——由数字、小数点和下划线组成 (1)整数文字 5,678,156E2,45_234_287(=45234287) (2)实数文字 188.993,88_670_551.453_909 (3)以数制基数表示的文字 格式:数制#数值# 例如: 10#170# 16#FE# 2#11010001# 8#376#

(4)物理量文字 例如:60s,100m 2. 字符串文字 字符——以单引号括起来的数字、字母和符号(ASCII码) 例如:’0’,’1’,’A’,’B’,’a’,’b’ 字符串——一维的字符数组,用双引号括起来。 (1)文字字符串 例如:”ABC”,”A BOY.”,”A”

(2)数值字符串——矢量 格式:数制基数符号“数值字符串” 其中: B——二进制基数符号; O——八进制基数符号; X——16进制基数符号; 例如: B“111011110”;矢量数组,长度为9 O“15”;等效B“001101”,长度为6 X“AD0”;等效B“101011010000”,长度为12

3. 标识符——是用户给常量、变量、信号、端口、子程序或参数定义的名字。VHDL的标识符由英文字母(A~Z,a~z)、数字(0~9)和下划线字符(_)组成。 • 短标识符必须遵守以下规则: (87标准) • 首写必须为英文字母 • 不区分大小写 • 最后一个字符不能为下划线 • 不允许连续出现两个下划线 • 关键字不能做为标识符 • 标识符最长为32个字符

例如: h_adder,mux21,example为合法标识符; 2adder,_mux21,ful__adder,adder_为错误的标识符。

VHDL’93标准支持扩展标识符,以反斜杠来定界,允许: ◎允许以数字开头 ◎允许两个以上的下划号 ◎允许使用空格和包含图形符号,但没有任何意义 ◎允许使用VHDL保留字 ◎区分字母大小写 ◎扩展标识符与短标识符不同,如aa与\aa\是不同的 ◎扩展标识符中如果有一个反斜杠,则用相邻的两个反斜杠来代替它 如:\74LS163\、 \Si&g_ _#N\(等价于\Sig__N\)、 \entity\、\ENTITY\、\74LS\\138\等为合法的标识符。

4. 下标名——数组 格式:标识符(表达式) 例如:b(3) 5. 段名——多个下标名的组合 格式:标识符(表达式 方向 表达式) 方向:TO——下标序号由低到高 DOWNTO——下标序号由高到低 例如:D(7 DOWNTO 0);表示数据总线D7~D0 D(0 TO 7 );表示数据总线D0~D7 6. 注释:--注释语

3.2.2 VHDL数据对象 ——存放各种类型数据的容器,包括变量、常量和信号 三种对象的物理含义: •常量代表数字电路中的电源、地、恒定逻 辑值等常数; •变量代表暂存某些值的载体,常用于描述算法; •信号代表物理设计中的某一条硬件连接线, 包括输入、输出端口。

1. 变量(VARIABLE) 规则:只能在进程(PROCESS)、函数(FUNCTION)和过程(PROCEDURE)中说明和使用的局域量。 定义格式: VARIABLE 变量名:数据类型[:=初始值] 例如:VARIABLE a:INTEGER VARIABLE b:INTEGER:=2; 注意:没有设定初始值的变量在仿真赋值时,系统会取默认值,字符型的取最大值,数值型的取最左或最小值。

变量赋值语句: 目标变量名:=表达式 例如:VARIABLE x,y:REAL VARIABLE a,b:BITVECTOR(0 TO 7); x:=100.0; y:=1.5+x; a:=“1010101” a(3 TO 6):=(‘1’,‘1’,‘0’,‘1’); a(0 TO 5):=b(2 TO 7);

2. 信号(SIGNAL) 规则:信号是在结构体(ARCHITECTURE)、程序包(PACKAGE)和实体中说明的全局量。 综合时初值被忽略 信号定义格式:SIGNAL 信号名:数据类型[:=初值]; 例如:SIGNAL temp:STDLOGIC:=‘0’; SIGNAL flaga,flagb:BIT SIGNAL data:STDLOGICVECTOR(15 DOWNTO 0);

信号赋值语句: 目标信号名<=表达式 例如:x<=9; y<=x; z<=x AFTER 5ns; 注意:1、信号是全局量,可在结构体、实体、块中说明和使用信号。而在进程和子程序中只能使用信号,不能说明信号。 2、端口是一种隐形的有方向的信号。即输出端口不能读数据,只能写入数据;输入端口不能写数据,只能读出数据。即:端口与信号的区别是in端口不能被赋值,out端口不能读数据。信号本身无方向,可读可写。

信号与变量的区别: (1)使用场合不同。变量只能在进程语句、函数语句和过程语句结构中说明和使用;信号通常在结构体、程序包和实体中说明。 (2)变量用“:=”号赋值,其值被立即使用(无时间延迟);而信号用“<=”赋值,其值一般经过一段时间的延迟后才能成为当前的赋值。 (3)变量不能表达“连线”或存储元件。 (4)信号代表连线,是电路内部硬件连接的抽象。作为连线,信号可以是逻辑门的输入或输出,也可以表达存储元件的状态。 (5)与变量不同,信号赋值可以利用after设置延时。

3. 常数(CONSTANT) 规则:常量必须在程序包、实体、结构体、块、子程序或进程的说明区域定义,且一旦被赋值就不能再改变。程序包中定义的常量可以在调用此程序包的所有设计实体(包括实体和结构体)中使用,具有最大的全局特征。 常数定义格式: CONSTANT 常数名:数据类型:=初值; 例如: CONSTANT fbus:BITVECTOR:=“010111”; CONSTANT Vcc:REAL:=5.0; CONSTANT delay:TIME:=25ns;

练习题1: 画出下面VHDL程序描述对应实体——七段显示器的逻辑图符号: ENTITY dec17s IS PORT ( q :in bit_vector(3 downto 0); led7s: out bit_vector(7 downto 0)); END ENTITY dec17s;

练习题2: 请根据下面的说明写出8D锁存器的实体说明,并画出对应的实体图符号: d[7..0]是8位D锁存器数据输入端,clk是时钟输入端,oe是三态使能控制输入端,高电平有效,clr是清零端,低电平有效, q[7..0]是输出端。

ENTITY scq8 IS PORT ( d: in std_logic_vector(7 downto 0); oe, clr: in bit; clk: in std_logic; q: out std_logic_vector(7 downto 0)); END ENTITY scq8;

练习题3: 判断下列标识符哪些是合法的? 3mux and21 half_ _adder port _orgate q_0 \hello\2008\ 合法的:and21、q_0

3.2.3 VHDL数据类型 • 标量型(Scalar Type)——单元素的 • 最基本数据类型 • (1)实数类型 • (2)整数类型 • (3)枚举类型 • (4)时间类型 2. 复合类型(Composite Type) (1)数组型(Array) (2)记录型(Record)

存取类型(Access Type)——为数据对象提供存取方式 • 类似于C语言中的指针类型,此指针可以是指向字符串,也可以指向地址。 • 存取类型只能用于仿真,不能被综合。 • 文件类型(Files Type)——提供多值存取类型 • 类似于C语言中的指向文件的指针类型。可以读取文件、文件中的一行,还可以读取行中的某些数据量。