Fibonacci Sequence

Fibonacci Sequence. Lecture L4.1 Lab 3. Fibonacci Sequence. 0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, 89, 144, 233,…. F (0) = 0 F (1) = 1 F ( n + 2) = F ( n ) + F ( n + 1) for all n ≥ 0. b a. a a + b. =. The Golden Rectangle. f =. a 2 = ab + b 2. 1 = f + f 2.

Fibonacci Sequence

E N D

Presentation Transcript

Fibonacci Sequence Lecture L4.1 Lab 3

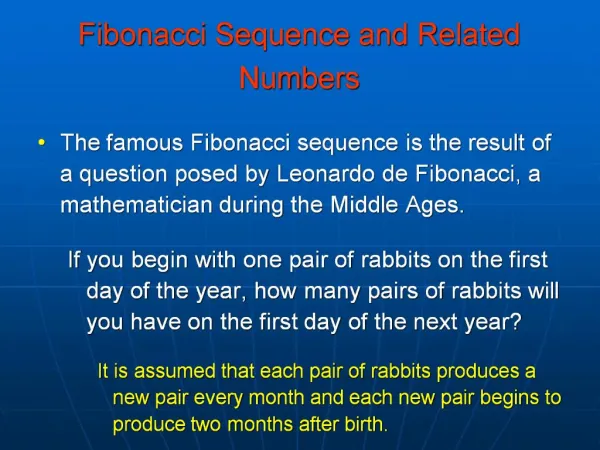

Fibonacci Sequence 0, 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, 89, 144, 233,… F(0) = 0 F(1) = 1 F(n + 2) = F(n) + F(n + 1) for all n ≥ 0.

b a a a + b = The Golden Rectangle f = a2 = ab + b2 1 = f + f2

Good Fibonacci Web Site http://www.mcs.surrey.ac.uk/Personal/R.Knott/Fibonacci/fibnat.html

-- Title: adder library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity adder is generic(width:positive); port ( A: in STD_LOGIC_VECTOR(width-1 downto 0); B: in STD_LOGIC_VECTOR(width-1 downto 0); S: out STD_LOGIC_VECTOR(width-1 downto 0) ); end adder; architecture adder_arch of adder is begin add1: process(A, B) begin S <= A + B; end process add1; end adder_arch; adder.vhd

regc.vhd -- Title: register with reset to 0 library IEEE; use IEEE.std_logic_1164.all; entity regc is generic(width: positive); port ( d: in STD_LOGIC_VECTOR (width-1 downto 0); load: in STD_LOGIC; reset: in STD_LOGIC; clk: in STD_LOGIC; q: out STD_LOGIC_VECTOR (width-1 downto 0) ); end regc;

regc.vhd architecture regc_arch of regc is begin process(clk, reset) begin if reset = '1' then for i in width-1 downto 0 loop q(i) <= '0'; end loop; elsif (clk'event and clk = '1') then if load = '1' then q <= d; end if; end if; end process; end regc_arch;

regs.vhd -- Title: register with reset to 1 library IEEE; use IEEE.std_logic_1164.all; entity regc is generic(width: positive); port ( d: in STD_LOGIC_VECTOR (width-1 downto 0); load: in STD_LOGIC; reset: in STD_LOGIC; clk: in STD_LOGIC; q: out STD_LOGIC_VECTOR (width-1 downto 0) ); end regc;

regs.vhd architecture regs_arch of regs is begin process(clk, reset) begin if reset = '1' then for i in width-1 downto 1 loop q(i) <= '0'; end loop; q(0) <= '1'; elsif (clk'event and clk = '1') then if load = '1' then q <= d; end if; end if; end process; end regs_arch;

fib_components.vhd -- A package containing component declarations -- for the Fibonacci counter library IEEE; use IEEE.std_logic_1164.all; package fib_components is component regs generic(width: positive); port ( d: in STD_LOGIC_VECTOR (width-1 downto 0); load: in STD_LOGIC; reset: in STD_LOGIC; clk: in STD_LOGIC; q: out STD_LOGIC_VECTOR (width-1 downto 0) ); end component;

fib_components.vhd (cont.) component regc generic(width: positive); port ( d: in STD_LOGIC_VECTOR (width-1 downto 0); load: in STD_LOGIC; reset: in STD_LOGIC; clk: in STD_LOGIC; q: out STD_LOGIC_VECTOR (width-1 downto 0) ); end component;

fib_components.vhd (cont.) component adder generic( width : POSITIVE); port( a : in std_logic_vector((width-1) downto 0); b : in std_logic_vector((width-1) downto 0); y : out std_logic_vector((width-1) downto 0)); end component; component binbcd port ( B: in STD_LOGIC_VECTOR (15 downto 0); P: out STD_LOGIC_VECTOR (15 downto 0)); end component; component x7seg Port ( x : in std_logic_vector(15 downto 0); cclk, clr : in std_logic; AtoG : out std_logic_vector(6 downto 0); A : out std_logic_vector(3 downto 0)); end component; end fib_components;

fib.vhd -- Title: Fibonacci Sequence library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.std_logic_unsigned.all; use work.fib_components.all; entity fib is port( mclk : in STD_LOGIC; bn : in STD_LOGIC; BTN4 : in STD_LOGIC; led: out std_logic; ldg : out STD_LOGIC; AtoG : out STD_LOGIC_VECTOR(6 downto 0); A : out STD_LOGIC_VECTOR(3 downto 0) ); end fib;

fib.vhd (cont.) architecture fib_arch of fib is -- System Library Components component IBUFG port ( I : in STD_LOGIC; O : out std_logic ); end component; signal s, r, t, p: std_logic_vector(15 downto 0); signal clr, clk, cclk, bnbuf, one, reset: std_logic; signal clkdiv: std_logic_vector(24 downto 0); constant bus_width: positive := 16;

fib.vhd (cont.) begin U00: IBUFG port map (I => bn, O => bnbuf); led <= bnbuf; ldg <= '1'; -- enable 74HC373 latch clr <= BTN4; -- Divide the master clock (50Mhz) process (mclk) begin if mclk = '1' and mclk'Event then clkdiv <= clkdiv + 1; end if; end process; clk <= bnbuf; cclk <= clkdiv(17); -- 190 Hz one <= '1';

fib.vhd (cont.) U1: adder generic map(width => bus_width) port map (a => t, b => r, y => s); R1: regs generic map(width => bus_width) port map (d => r, load =>one, reset => reset, clk =>clk, q => t); W1: regc generic map(width => bus_width) port map (d => s, load => one, reset => reset, clk =>clk, q => r); U2: binbcd port map (B => r, P => p); U3: x7seg port map (x => p, cclk => cclk, clr => clr, AtoG => AtoG, A => A); end fib_arch;

Verilog adder.v // Title: adder module adder(a,b,y); parameter width = 4; input [width-1:0] a; input [width-1:0] b; output [width-1:0] y; reg [width-1:0] y; always @(a, b) begin y = a + b; end endmodule

regc.v // Title: register with reset to 0 module regc(d,load,reset,clk,q); parameter width = 4; input [width-1:0] d; input load, reset, clk; output [width-1:0] q; integer i; reg [width-1:0] q; always @(posedge clk or posedge reset) begin if(reset) q <= 0; else if(load) q <= d; end endmodule

regs.v // Title: register with reset to 1 module regs(d,load,reset,clk,q); parameter width = 4; input [width-1:0] d; input load, reset, clk; output [width-1:0] q; integer i; reg [width-1:0] q; always @(posedge clk or posedge reset) begin if(reset) q <= 1; else if(load) q <= d; end endmodule

fib.vhd // Title: Fibonacci Sequence module fib(mclk, bn, BTN4, led, ldg, AtoG, A); input mclk, bn, BTN4; output led; output [6:0] AtoG; output [3:0] A; wire [6:0] AtoG; wire [3:0] A; wire clr, cclk, bnbuf; reg [24:0] clkdiv; wire [15:0] s, r, t, p;

IBUFG U00 (.I (bn), .O (bnbuf)); assign led = bnbuf; assign clr = BTN4; assign clk = bnbuf; // Divide the master clock (50Mhz) always @(posedge mclk) begin clkdiv <= clkdiv + 1; end assign cclk = clkdiv[17]; // 190 Hz assign one = 1;

defparam U1.width = 16, R1.width = 16, W1.width = 16 ; adder U1(.a(t),.b(r),.y(s)); regs R1(.d(r),.load(one),.reset(reset),.clk(clk),.q(t)); regc W1(.d(s),.load(one),.reset(reset),.clk(clk),.q(r)); binbcd U2(.B(r),.P(p)); x7seg U3(.x(p),.cclk(cclk),.clr(clr),.AtoG(AtoG),.A(A)); endmodule