Summary

Summary. Current density in a signal line was estimated, based on the simple circuit shown in Fig.1. This circuit is scaled down according to ITRS 2003. Wire of the signal line is assumed to be a intermediate wire. Wire length is assumed to be (wire pitch) x 200.

Summary

E N D

Presentation Transcript

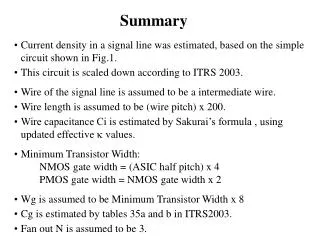

Summary • Current density in a signal line was estimated, based on the simple circuit shown in Fig.1. • This circuit is scaled down according to ITRS 2003. • Wire of the signal line is assumed to be a intermediate wire. • Wire length is assumed to be (wire pitch) x 200. • Wire capacitance Ci is estimated by Sakurai’s formula , using updated effective k values. • Minimum Transistor Width: NMOS gate width = (ASIC half pitch) x 4 PMOS gate width = NMOS gate width x 2 • Wg is assumed to be Minimum Transistor Width x 8 • Cg is estimated by tables 35a and b in ITRS2003. • Fan out N is assumed to be 3.

Average Imax = f *(Cg*Wg *N+Ci) *Vdd Average Imax (via) = Average Imax A Model for the Calculation - Tr width=Min Tr width x 8 Vdd Cg*Wg Imax Ci Intermediate wire(L=wire pitch x 200) Cg*Wg Fan out N=3

Calculation of Average Jmax (based on ITRS2003) Based on 2003 road map (Rev.1) Year 2003 2004 2005 2006 2007 2008 2009 2012 2015 2018 Technology node MPU/ASIC 1/2pitch 107 90 80 70 65 57 50 35 25 18 Width(nm) @Intermediate 160 137.5 120 107.5 97.5 87 78 55 39 27.5 Height(nm) @Intermediate 272 233.75 204 182.75 175.5 156.6 140.4 104.5 74.1 55 Vdd (V) 1.2 1.2 1.1 1.1 1.1 1 0.9 0.8 0.7 x 1 Gate Width (mm)* 1.284 1.08 0.96 0.84 0.78 0.684 0.6 0.42 0.3 0.216 x 8 Gate width = Wg (mm) 10.272 8.640 7.680 6.720 6.240 5.472 4.800 3.360 2.400 1.728 Physical gate length (mm)** 0.045 0.037 0.032 0.028 0.025 0.022 0.020 0.014 0.010 0.007 Inversion Gate Dielectric Value (nm)** 2.100 2.000 1.800 1.700 1.300 1.200 1.200 1.100 1.000 0.900 Parasitic Fringe/Overlap Cap (fF/mm) 0.240 0.240 0.240 0.230 0.220 0.200 0.190 0.150 0.120 0.080 Cg @ W=1mm(fF/mm) 0.979 0.878 0.853 0.798 0.883 0.833 0.765 0.589 0.465 0.348 Cg x Wg (fF) 10.059 7.588 6.554 5.364 5.513 4.555 3.672 1.979 1.116 0.602 Frequency (MHz)*** 3088 3990 5173 5631 6739 8330 9920 16735 25616 35020 Fan out : N 3.000 3.000 3.000 3.000 3.000 3.000 3.000 3.000 3.000 3.000 Wire capacitance (fF/mm) 0.205 0.199 0.199 0.198 0.174 0.174 0.174 0.151 0.120 0.110 Wire length :Pitch*200 (mm) 64.000 55.000 48.000 43.000 39.000 34.800 31.200 22.000 15.600 11.000 Total Wire Cap (fF) 13.109 10.939 9.547 8.509 6.790 6.059 5.432 3.321 1.864 1.212 Total Cap (fF) 43.287 33.704 29.208 24.602 23.328 19.725 16.448 9.259 5.212 3.017 Average Imax(nA) 160405 161373 166202 152385 172929 195671 275254 213460 146026 73967.9 Average Jmax (MA/cm^2) 0.369 0.502 0.679 0.776 1.011 1.436 2.513 3.714 5.053 4.890 * Minimum NMOS gate width= (ASIC half pitch)*4, Minimum PMOS gate width=NMOS gate width*2 ** from Table 35a and 35b **: from Table 4c( not updated)

4.5 Calculated based on delay time using typical critical path 4.0 Estimated by typical low-k materials and ILD structures k=3.0-3.3 Described in roadmap table at ITRS2002 3.5 k=2.6-3.0 Effective Dielectric Constant; keff 3.0 k=2.4-2.8 2.5 k=2.0-2.4 2.0 Solutions exist or being optimized Solutions are known Red Brick Wall (Solutions are NOT known) k<1.7 1.5 14 02 03 04 05 06 07 08 09 10 11 12 13 Year of 1st Shipment (=ES) ITRS2003 keff Roadmap Revision

wire wire repeater Critical Path in High-end SoC and RC-scaling Scenario <long IM> <long GM> <short IM> GM with reverse scaled width and thickness wire wire wire wire wire repeater Typical circuits(2NAND+Inv.) connected with average long- intermediate(IM) wires having multiple-stages Global metal(GM) wires with chip-size length divided by optimized repeaters IM wires with module-size length divided by optimized repeaters tmin(1/fmax) µ RTCW+RWCT+2ÖRWCWRTCT Scaling of both RW and CW should be steadily done in order to improve speed (t min) by 30% per generation.

Assumption on Interconnect Parameter Estimation Model <Assumption on Interconnect parameter estimation> Design rule x0.70/node-scaling, Reverse-scaling for GM Chip-size const.(=7mm sq.) as 1-clock cycle limit Module-size x 0.70/node-scaling Repeater Inserted for long IM and GM wires Gate density x 2.0/node(based on ITRS2002 MPU-R.M) Active power density x 0.6/node with average-long IM wire Logic depth x 0.75/node-scaling t min. x 0.70/node-scaling

Impacts of Varying Assumption on Interconnect Parameter < Impact on interconnect parameter > Chip-size RC delay increases, lower keff and r eff are needed Module-size RC delay increases, lower keff and r eff are needed Repeater¯ RC delay drastically increases for long IM and GM wire Total wire length (= number of layers) increases RC delay increases, lower keff and r eff are needed Gate density Power density Lower keff is needed, Jmax/Imax increase Logic depth Lower keff and r eff are needed for IM wire

1 1 1 1 1 1 1 1 1 1 - - - - - 1 7 2 1 6 9 a p a C 1 6 6 l a t o T 1 6 3 1 6 0 B f _ t C a p _ t C a p _ k T r _ I L D _ k V i a _ I L D _ k Sensitivity Analysis of Interconnect Parameters on keff A,C B,C C D Cu Cu Cu D B A: DCL-thickness B: DPL-thickness C: DPL(or DCL)-k D: ILD(Trench)-k E: ILD(Via)-k E A B C E B D A E A B A C Cu D E B D E B C D E M a i n E f f e c t s P l o t ( d a t a m e a n s ) f o r T o t a l C a p a DCL:Dielectric Capping Layer DPL:Dielectric Protection Layer A C D E A C D A B D A B C D C E C D E C D B E B C E • Most sensitive to k of both DPL and DCL • Sensitive to DPL thickness as well as k of ILD (Trench, Via) • Should reduce k and thickness of DPL and DCL as well as k of ILD B C D A D E A D A C E A B E A B C D E A B D E A B C E A B C D E 0 5 1 0

90 nm Node Solutions (2004) Assumptions Cu Cap height = 50nm Hardmask height = NA Via height = 210nm Trench height = 230nm Minimum L/S = 140nm Assumptions Cu Cap height = 50nm Hardmask height = 50nm Via height = 210nm Trench height = 230nm Minimum L/S = 140nm Assumptions Cu Cap height = 50nm Hardmask height = 50nm Via height = 210nm Trench height = 230nm Minimum L/S = 140nm Assumptions k(Cu Cap) = 5.0 k(Hardmask) = NA k(via) = 3.0 k(trench) = 3.0 keff = 3.30 Assumptions k(Cu Cap) = 5.0 k(Hardmask) = 4.1 k(via) = 2.65 k(trench) = 2.65 keff = 3.14 Assumptions k(Cu Cap) = 5.0 k(Hardmask) = 4.1 k(via) = 3.7 k(trench) = 2.65 keff = 3.63

65 nm Node Solutions (2007) Assumptions Cu Cap height = 35nm Hardmask height = NA Via height = 150nm Trench height = 170nm Minimum L/S = 100nm Assumptions Cu Cap height = 35nm Hardmask height = 35nm Via height = 150nm Trench height = 170nm Minimum L/S = 100nm Assumptions Cu Cap height = 35nm Hardmask height = 35nm Via height = 150nm Trench height = 170nm Minimum L/S = 100nm Assumptions k(Cu Cap) = 4.0 k(Hardmask) = NA k(via) = 2.8 k(trench) = 2.8 keff = 2.96 Assumptions k(Cu Cap) = 4.0 k(Hardmask) = 3.0 k(via) = 2.65 k(trench) = 2.65 keff = 2.83 Assumptions k(Cu Cap) = 4.0 k(Hardmask) = 3.0 k(via) = 2.5 k(trench) = 2.4 keff = 2.71

45 nm Node Solutions (2010) Assumptions Cu Cap height = 25nm Hardmask height = NA Via height = 110nm Trench height = 125nm Minimum L/S = 70nm Assumptions Cu Cap height = 25nm Hardmask height = 25nm Via height = 110nm Trench height = 125nm Minimum L/S = 70nm Assumptions Cu Cap height = 25nm Hardmask height = 25nm Via height = 110nm Trench height = 125nm Minimum L/S = 70nm Assumptions k(Cu Cap) = 3.5 k(Hardmask) = NA k(via) = 2.4 k(trench) = 2.4 kkeff = 2.54 Assumptions k(Cu Cap) = 3.5 k(Hardmask) = 2.5 k(via) = 2.2 k(trench) = 2.2 keff = 2.40 Assumptions k(Cu Cap) = 3.5 k(Hardmask) = 2.5 k(via) = 2.2 k(trench) = 2.0 keff = 2.31

Cu Resistivity Increase by Electron-scattering Effect Wire width < mean free path of electrons ¯ Surface scattering dominant p=0 (complete diffuse scattering) p=1 (specular scattering) ¯ Resistivity increases even if Barrier metal is set to zero ¯ BM/Cu interface roughness reduction might be a solution 5 Measured Cu resistivity without BM p=0 4 3 Resistivity(mWcm) p: fraction of electrons having elastic collisions at wire surfaces 2 p=0.5 1 0 0 0.1 0.2 0.3 0.4 0.5 Line width(nm) Red collar legend (Red brick wall) beyond 32nm node (IM pitch=95nm)