基本描述语句小结

基本描述语句小结. 顺序语句 wait 等待 if_else 条件执行 case 条件选择 for_loop 循环 next 跳出循环 exit 循环结束 信号代入语句、过程调入语句、断言语句即可以作为顺序语句,也可作为并行语句。即它们出现在进程、过程和函数之外时应视为并行语句,否则为顺序语句。. 并行语句. Process 语句 并行信号代入 : Q<=aANDb AFTER 5ns; 条件信号代入 : q<=b0 WHEN sel=“0” 选择信号代入 : WITH sel SELECT

基本描述语句小结

E N D

Presentation Transcript

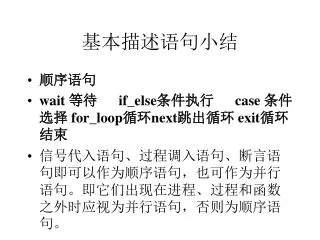

基本描述语句小结 • 顺序语句 • wait 等待 if_else条件执行 case 条件选择 for_loop循环next跳出循环 exit循环结束 • 信号代入语句、过程调入语句、断言语句即可以作为顺序语句,也可作为并行语句。即它们出现在进程、过程和函数之外时应视为并行语句,否则为顺序语句。

并行语句 • Process 语句 • 并行信号代入:Q<=aANDb AFTER 5ns; • 条件信号代入:q<=b0 WHEN sel=“0” • 选择信号代入:WITH sel SELECT • q<=b0 WHEN a=“0” • ELSE • q<=b1 WHEN a=“1”

并行过程调用[过程标号:]过程名(参数表) • 块语句 :(见下例) • 块标号名: BLOCK • 块头定义{说明语句} • BEGIN • {并发处理语句} • EDN BLOCK 标号名 • 并行断言语句ASSERT 条件 [报告信息][SECVERITY 出错级别] • ASSERT (a<256) REPORT ”a out of range” • SEVERITY error

一个包含有半加法器和半减法器的电路, Sum=A XOR B Carry=A AND B Difference=A XOR B Borrow=NOTA AND B 程序: ENTITY CH3_3_1 is PORT(A,B : IN Std_Logic; Carry,Sum,Borrow,Difference:OUT Std_Logic ); END CH3_3_1;

ARCHITECTURE a OF CH3_3_1 IS BEGIN Half_Adder : Block -- Half Adder Begin Sum <= A Xor B; Carry <= A and B; End Block Half_Adder; Half_Subtractor: Block -- Half Subtractor Begin Difference <= A Xor B; Borrow <= Not A and B; End Block Half_Subtractor; END a;

掌握层次设计的方法 • 将设计任务分成若干模块,规定每个模块的功能和各模块之间的接口。 • 各模块单独调试。 • 最后将各模块汇总连调。 • 计数模块(60,24) • 控制模块 • 扫描模块 显示驱动模块 ······

-- ******************************************** LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; --7段显示器电路设计 ********************************************* ENTITY Display is PORT( CP : IN STD_LOGIC; -- CLOCK NUMIN : IN STD_LOGIC_VECTOR(3 DOWNTO 0); -- input Number Display Signal SEGOUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); -- SEG7 Display O/P SELOUT : OUT STD_LOGIC_VECTOR(5 DOWNTO 0) -- Select SEG7 6bit O/P ); END Display; --********************************************* ARCHITECTURE a OF Display IS SIGNAL SEG : STD_LOGIC_VECTOR( 6 DOWNTO 0); -- SEG7 Display Signal SIGNAL SEL : STD_LOGIC_VECTOR( 5 DOWNTO 0); -- Select SEG7 Signal BEGIN Connection : Block Begin SELOUT <= SEL; -- Seg7 Disp Selection SEGOUT(6 DOWNTO 0) <= SEG; -- Seven Segment Display SEGOUT(7) <= '0'; -- p not Display End Block Connection; Free_Counter : Block -- 计数器 -- 产生扫描信号 Signal Q : STD_LOGIC_VECTOR(24 DOWNTO 0); Signal S : STD_LOGIC_VECTOR(2 DOWNTO 0); Begin PROCESS (CP) -- 计数器计数 Begin IF CP'Event AND CP='1' then --input >24 ~250 Hz Q <= Q+1; END IF; END PROCESS; S <= Q(1 DOWNTO 0); --about INPUT 50~200 Hz --扫描信号 SEL <= "111110" WHEN S=0 ELSE "111101" WHEN S=1 ELSE "111011" WHEN S=2 ELSE "110111" WHEN S=3 ELSE "101111" WHEN S=4 ELSE "011111" WHEN S=5 ELSE "111111"; End Block Free_Counter; SEVEN_SEGMENT : Block -- Binary Code -> Segment 7 Code Begin --gfedcba SEG <= "0111111" WHEN NUMIN = 0 ELSE "0000110" WHEN NUMIN = 1 ELSE "1011011" WHEN NUMIN = 2 ELSE "1001111" WHEN NUMIN = 3 ELSE "1100110" WHEN NUMIN = 4 ELSE "1101101" WHEN NUMIN = 5 ELSE "1111101" WHEN NUMIN = 6 ELSE "0000111" WHEN NUMIN = 7 ELSE "1111111" WHEN NUMIN = 8 ELSE "1101111" WHEN NUMIN = 9 ELSE "1110111" WHEN NUMIN = 10 ELSE "1111100" WHEN NUMIN = 11 ELSE "0111001" WHEN NUMIN = 12 ELSE "1011110" WHEN NUMIN = 13 ELSE "1111001" WHEN NUMIN = 14 ELSE "1110001" WHEN NUMIN = 15 ELSE "0000000"; End Block SEVEN_SEGMENT; END a;

除24计数电路--******************************************************除24计数电路--****************************************************** LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; --****************************************************** ENTITY COUNTER24 IS PORT( CP : IN STD_LOGIC; --时钟脉冲 BIN : OUT STD_LOGIC_VECTOR (5 DOWNTO 0); --计数输二进 出制? S : IN STD_LOGIC; --输出启动信号 CLR : IN STD_LOGIC; --清除信号 EC : IN STD_LOGIC; --使能计数信号 CY24 : OUT STD_LOGIC --计数24进位信号 ); END COUNTER24; --******************************************************* ARCHITECTURE a OF COUNTER24 IS SIGNAL Q : STD_LOGIC_VECTOR (4 DOWNTO 0) ; SIGNAL RST, DLY : STD_LOGIC; BEGIN PROCESS (CP,RST) -- 计数24 BEGIN IF RST = '1' THEN Q <= "00000"; -- 复位计数器 ELSIF CP'event AND CP = '1' THEN DLY <= Q(4); IF EC = '1' THEN Q <= Q+1; -- 计数值加1 END IF; END IF; END PROCESS; CY24 <= NOT Q(4) AND DLY; -- 进位信号微分 RST <= '1' WHEN Q=24 OR CLR='1' ELSE -- 复位信号设定 '0'; BIN <= ('0' & Q) WHEN S = '1' ELSE -- 计数输出 "000000"; END a;

除60计数电路 --****************************************************** LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; --****************************************************** ENTITY COUNTER60 IS PORT( CP : IN STD_LOGIC; --时钟脉冲 BIN : OUT STD_LOGIC_VECTOR (5 DOWNTO 0); --计数60二进制 S : IN STD_LOGIC; --输出启动信号 S : IN STD_LOGIC; --输出启动信号 CLR : IN STD_LOGIC; --清除信号 EC : IN STD_LOGIC; --使能计数信号 CY60 : OUT STD_LOGIC --计数60进位信号 ); END COUNTER60; --******************************************************* ARCHITECTURE a OF COUNTER60 IS SIGNAL Q : STD_LOGIC_VECTOR (5 DOWNTO 0) ; SIGNAL RST, DLY : STD_LOGIC; BEGIN PROCESS (CP,RST) -- 计数60 BEGIN IF RST = '1' THEN Q <= "000000"; -- 复位计数器 ELSIF CP'event AND CP = '1' THEN DLY <= Q(5); IF EC = '1' THEN Q <= Q+1; -- 计数值加1 END IF; END IF; END PROCESS; CY60 <= NOT Q(5) AND DLY; -- 进位信号微分 RST <= '1' WHEN Q=60 OR CLR='1' ELSE -- 复位信号设定 '0'; BIN <= Q WHEN S = '1' ELSE -- 计数输出 "000000"; END a;

微分电路 -- ******************************************** LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; --********************************************* ENTITY Ch6_2_2 is PORT( A,CP : IN STD_LOGIC; UP_OP,DN_OP,DL_OP : OUT STD_LOGIC ); END Ch6_2_2; --********************************************* ARCHITECTURE a OF Ch6_2_2 IS SIGNAL Q1,Q2 : STD_LOGIC; BEGIN -- *** Time Delay PROCESS (CP) BEGIN IF CP'event AND CP='1' THEN Q2 <= Q1; -- 2rd Stage Q1 <= A; -- 1st Stage D Flip/Flop END IF; END PROCESS; -- *** Time Delay UP_OP <= Q1 AND NOT Q2; -- ** Differential DN_OP <= NOT Q1 AND Q2; DL_OP <= Q1 XOR Q2; -- ** Differential END a;

按键弹跳消除电路 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; --************************************************************** ENTITY Debunce is PORT( CP : IN STD_LOGIC; -- CLOCK Key : IN STD_LOGIC; -- Input Signal DLY_OUT : OUT STD_LOGIC; -- Debounce O/P DIF_OUT : OUT STD_LOGIC -- Differential O/P ); END Debunce; --************************************************************** ARCHITECTURE a OF Debunce IS SIGNAL SAMPLE, DLY, NDLY, DIFF : STD_LOGIC; -- Binary BEGIN Free_Counter : Block -- 计数器 & 产生扫描信号 Signal Q : STD_LOGIC_VECTOR(14 DOWNTO 0); Signal D0 : STD_LOGIC; Begin PROCESS (CP) -- 计数器计数 Begin IF CP'Event AND CP='1' then D0 <= Q(14); Q <= Q+1; END IF; END PROCESS; SAMPLE <= Q(14) AND NOT D0; --产生125HZ脉冲 --SAMPLE <= Q(1) AND NOT D0; END Block Free_Counter; Debunce : Block -- Debounce SIGNAL D0, D1, S, R : STD_LOGIC; Begin Process (CP) Begin IF CP'EVENT AND CP='1' THEN IF SAMPLE = '1' THEN D1 <= D0; D0 <= KEY; -- Two Stage Delay S <= D0 AND D1; -- Generate S、R R <= NOT D0 AND NOT D1; END IF; END IF; End Process; DLY <= R NOR NDLY; -- Debounce O/P NDLY <=S NOR DLY; DLY_OUT <= DLY; End Block Debunce; Differential : Block -- Differential Signal D1,D0 : STD_LOGIC; BEGIN Process (CP) Begin IF CP'EVENT AND CP='1' THEN D1 <= D0; D0 <= DLY;-- Two State Delay END IF; End Process; DIFF <= D0 AND NOT D1; -- Differential END Block Differential; DIF_OUT <= DIFF; -- Differential O/P END a;

采用元件编辑器进行整体熔合 • 模块之间的连接,接口的熔合。 • 最后结果的仿真(实物电路上的调整)