3.1 積體電路層

500 likes | 710 Vues

3.1 積體電路層. ρ:resitivity, σ:conductivity, Rs:Sheet Resistance. R=ρ(L/A)=(1/σ)(L/Wt)=(1/σt)=ρ/t=Rs (L=W). Rl=Rs*n ; n=L/W. C=ε ox (wl/Tox), ε ox =3.9ε o ;ε o =8.854*10 -14 F/cm. 3.2 MOSFET. n n =N d -N a ;P p =N a -N d. np =n i 2 (mass-action law) Ex3.1;3.2(P.3-14,15).

3.1 積體電路層

E N D

Presentation Transcript

ρ:resitivity, σ:conductivity, Rs:Sheet Resistance R=ρ(L/A)=(1/σ)(L/Wt)=(1/σt)=ρ/t=Rs (L=W)

nn=Nd-Na ;Pp=Na-Nd np=ni2 (mass-action law) Ex3.1;3.2(P.3-14,15) σ=q(unn+upp)=1/ρ, σ:conductivity, u:mobility

Rn=1/βn(VG-Vtn) βn=unCox(W/L)

Rp=1/β p(VG-|Vtp|) βp=upCox(W/L)

C之效應 • Time Delay • Power Dissipation

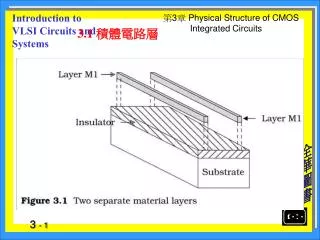

3.3CMOS各層 FOX: Field Oxide 場氧化物 Layers: 1. P-sub(基板) 2. n-well(井區) 3. Gate Oxide 4.Gate(poly-Si) 5.n+ 6.p+7.Contact 8.Metal

1. M1~M5間以SiO2隔離 ; M1~M5間以Via連結(銅) 2. 元件用Contact與外面M1作連結 (材質:W鎢)

Vin IC Design:CMOS Inverter (a) NMOS PMOS Vout Shallow trench isolation (STI) • P-channel active region • P-channel Vt • P-channel LDD • P-channel S/D • N-channel active region • N-channel Vt • N-channel LDD • N-channel S/D (b) P-well N-well Polycide gate and local interconnection Metal 1 Contact Metal 1, AlCu W PMD n n p p + + + + STI (c) P-Well N-Well P-Epi P-Wafer

IC Design: Layout and Masks of CMOS Inverter CMOS inverter layout Mask 1, N-well Mask 2, P-well Mask 3, shallow trench isolation Mask 4, 7, 9, N-Vt, LDD, S/D Mask 5, 8, 10, P-Vt, LDD, S/D Mask 6, gate/local interconnection Mask 11, contact Mask 12, metal 1

VDD ,VSS使用Metal連接 • n+與p+差別;p+有well • Metal與n+或p+連接必須使用Contact

F=BAR(xy+zw) Bugs? 6 errors

Exercise (P3-46) • 1,2,3,5,6,8,10,11,12,13,14,15,16,18,19