Processor Selection in S3E2S Environment: A Comprehensive Approach

260 likes | 366 Vues

This paper presents a systematic methodology for synthesizing and selecting processors within the S3E2S environment. We discuss application and processor characteristics, followed by an in-depth case study showcasing the PODOS integration algorithm. The study outlines how applications can be characterized by their instruction types, memory access, and execution profiles, ultimately leading to effective processor mapping based on a library of various processor types, including CISC, RISC, and DSPs. The conclusions highlight the benefits of this selective approach for embedded electronic systems.

Processor Selection in S3E2S Environment: A Comprehensive Approach

E N D

Presentation Transcript

System synthesis and processor selection in the S3E2S environment Márcio Kreutz, Luigi Carro, Flávio Wagner, Marcio Oyamada SBCCI 99 Natal

1 Outline • Introduction • Application and Processors characteristics • Processors selection • Case study • Conclusions

2 • Specification, simulation and synthesis of embedded electronic systems • Distributed OO modeling • Whole system behaviour described • Granularity defined by user as C++ functions • Abstract behaviours • Decomposed into Digital Objects (DO) or Analogic Objects (AO). • DO mapped to processors Introduction

3 Application Modeling SIMOO MET (Model Editor Tool)

4 C++ function specification

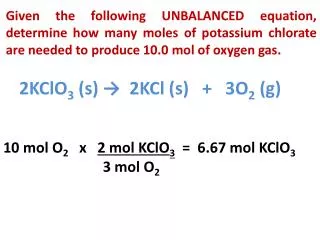

5 Application characterization • An application can be defined by its instructions types: • control jump, branch, conditional br.; • memory access load, store; and • processing operations add, or, mult

6 Application characteristics • Type of data used • Size of required binary word • Maximum allowed execution time • Number of requested basic blocks (i.e., contiguous instructions without a branch) • Number of instructions in each basic block • Number of data points, and how they are stored • (local memory, register, large size memory) • Number of memory acc. in each basic block • Data dependencies

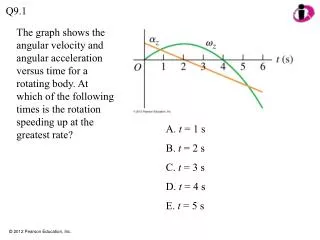

7 Control: PPC = C C + M + P Memory: PPM = M C + M + P Processing: PPP = P C + M + P Functions mapping to processors • Application and Performance profiles • Processor characteristics testing according to the instructions types as:

8 Processors characteristics • Size of binary word • Types of instructions • Memory operand accessing modes • Execution time of each instruction, in clock Cycles • Number of busses to access memory • Type of memory • Number of registers • Control instructions • Use of pipeline and depth of eventual pipeline • Use of harvard architecture or not

9 Characteristics of tested Processors

10 Processor selection block diagram Simulation SIMOO Classes Digital Objects Processors characteristics CDFG PP for each processor Mapping

11 Processor selection • Processor library • each one with specific characterisitics • CISC, RISC, DSP, microcontrollers, ... • How does each processor execute a function behaviour ?? • Creation of a CDFG for all functions • to get the application and performance profiles

12 PODOS integration CDFG Control Loop Acel_h Acel_v Acel_h Acel_v MUL MUL Int2 Int1 ADD Data flow Int3 CALL Vel_prev Vel1 ADD ATTRIB 2 Int4 DIV Vel_prev Int5 Tsampling Control MUL Processing mean ATTRIB Memory access vel

13 Case study PODOS Integration algorithm for(int i; i < n; i++) { vel1= sqrt((acel_v*acel_v) + (acel_h*acel_h)); mean = (((vel_prev + vel1)/2) * Tsampling); vel_prev= vel1; vel = mean; }

14 Case study PODOS Integration algorithm Memory accesses: 4 READ and 2 WRITE for(int i; i < n; i++) { vel1= sqrt((acel_v*acel_v) + (acel_h*acel_h)); mean = (((vel_prev + vel1)/2) * Tsampling); vel_prev= vel1; vel = mean; } Memory access cycles 8051 Risco C25 6 * 2 2 1 12 12 6 / 2 buses = 3

15 Case study PODOS Integration algorithm 7 REG accesses for(int i; i < n; i++) { vel1= sqrt((acel_v*acel_v) + (acel_h*acel_h)); mean = (((vel_prev + vel1)/2) * Tsampling); vel_prev= vel1; vel = mean; }

16 Case study PODOS Integration algorithm 3 MULT operation for(int i; i < n; i++) { vel1= sqrt((acel_v*acel_v) + (acel_h*acel_h)); mean = (((vel_prev + vel1)/2) * Tsampling); vel_prev= vel1; vel = mean; } Processing cycles 8051 Risco C25 3 * 48 1 1 96 3 3

17 Case study PODOS Integration algorithm 1 DIV operation for(int i; i < n; i++) { vel1= sqrt((acel_v*acel_v) + (acel_h*acel_h)); mean = (((vel_prev + vel1) / 2) * Tsampling); vel_prev= vel1; vel = mean; } Processing cycles 8051 Risco C25 1* 48 1 1 48 1 1

18 Case study PODOS Integration algorithm 3 ADDs for(int i; i < n; i++) { vel1= sqrt((acel_v*acel_v) + (acel_h*acel_h)); mean = (((vel_prev + vel1)/2) * Tsampling); vel_prev= vel1; vel = mean; } Processing cycles 8051 Risco C25 3* 3 1 1 9 3 3

19 Case study PODOS Integration algorithm 2 ATTRIB for(int i; i < n; i++) { vel1= sqrt((acel_v*acel_v) + (acel_h*acel_h)); mean = (((vel_prev + vel1)/2) * Tsampling); vel_prev= vel1; vel = mean; } Processing cycles 8051 Risco C25 2* 3 1 1 6 2 2

20 Case study PODOS Integration algorithm 2 Control operations for(int i; i < n; i++) { vel1= sqrt((acel_v*acel_v) + (acel_h*acel_h)); mean = (((vel_prev + vel1)/2) * Tsampling); vel_prev= vel1; vel = mean; } Control cycles 8051 Risco C25 2* 3 1 4 6 2 8

Podos Integration results 21 Performance Profiles

Digital Filter results 22 Performance Profiles

Dot Product Results 23 Performance Profiles

24 Conclusions • Synthesis based on a library of processors • Exploration of the characteristics of all • function presented in application • Mapping to processors made through • processors characteristics • multiprocessor system

25 Future works • Distributed protocol selection and • synthesis • Merge objects in processors • Code generation • SIMOO MET integration

![CP = E[ s 2 , s 5 , s 1 , s 3 , s 2 ’ , s 3 ’ , s 4 , s 1 ’ , s 4 ’ , s 5 ’ ] S[] I[]](https://cdn3.slideserve.com/6546826/slide1-dt.jpg)

![(E)-(S)-4-[(S)-4-Methyl-2-((S)-3-methyl-2{(S)-2-[(5-methyl-isoxazole-3- carbonyl)-amino]-propionylamino}-butyrylamino)-p](https://cdn5.slideserve.com/9969977/e-s-4-s-4-methyl-2-s-3-methyl-2-s-2-5-methyl-dt.jpg)