MICA Node Architecture

MICA Node Architecture. WEBS retreat Jason Hill 1/14/2002. Objective. To produce an experimental platform for the NEST research teams to use explore design tradeoffs in embedded networked devices. Must be ready to deliver nodes in January 2002.

MICA Node Architecture

E N D

Presentation Transcript

MICA Node Architecture WEBS retreat Jason Hill 1/14/2002

Objective • To produce an experimental platform for the NEST research teams to use explore design tradeoffs in embedded networked devices. • Must be ready to deliver nodes in January 2002. All parts used must be available in quantity by Nov. 01 Development tools must be readily accessible

Outline • Previous designs and factors motivating new design • Mica Architecture and Hardware Details • Architectural Implications (RADIO, CPU interface) • Performance characteristics in key areas • Future directions

Previous Designs • MICA is the 4th generation of the Berkeley Motes. • COTS dust prototypes, by Seth Hollar • weC Mote • Rene Mote, manufactured by Crossbow 3.1 Dot mote, used for IDF

Rene Shortcomings • Insufficient memory size • code size limitation the tightest • “29 Palms” and “Cory Hall” barely fit • Radio performance erratic, slow • Tied to battery voltage • No way to determine battery levels • Unpredictable operation • Awkward attachment to power supply • No unique Ids • IDF required manual assignment

Goals • More storage • More communication bandwidth • Stabilize board voltage • More capability available to sensor boards • Retain “cubic inch” form factor and AA/year power budget with clean package. • Allow opportunities for flexible communication protocols • time synchronization • other algorithms

The MICA architecture 51-Pin I/O Expansion Connector • Atmel ATMEGA103 • 4 Mhz 8-bit CPU • 128KB Instruction Memory • 4KB RAM • 4 Mbit flash (AT45DB041B) • SPI interface • 1-4 uj/bit r/w • RFM TR1000 radio • 50 kb/s – ASK • Focused hardware acceleration • Network programming • Same 51-pin connector • Analog compare + interrupts • Same tool chain Digital I/O 8 Analog I/O 8 Programming Lines Atmega103 Microcontroller DS2401 Unique ID Coprocessor Transmission Power Control Hardware Accelerators SPI Bus TR 1000 Radio Transceiver 4Mbit External Flash Power Regulation MAX1678 (3V) Cost-effective power source 2xAA form factor

Major features • 16x program memory size (128 KB) • 8x data memory size (4 KB) • 16x secondary storage (512 KB) • 5x radio bandwidth (50 Kb/s) • 6 ADC channels available • Same processor performance

Major Features (cont.) • Allows for external SRAM expansion • Provides sub microsecond RF synchronization primitive • Provides unique serial ID’s • On-board DC booster • Remains Compatible with Rene Hardware and current tool chain

Microcontroller Alternatives • Atmega 163 • same pin out as RENE • 2x memory • Can self-reprogram • ARM Thumb • lower power consumption, lower voltage • greater performance • poor integration slow radio • TI MSP340 • Superior performance • 1/10 power consumption • Better integration Not enough memory Peripheral support missing No GCC, tool chain missing

Radio • Retained RFM TR1000 916 Mhz radio • Able to operate in OOK (10 kb/s) or ASK (115 kb/s) mode • Design SPI-based circuit to drive radio at full speed • full speed on TI MSP, 50 kb/s on ATMEGA • Improved Digitally controlled TX strength DS1804 • 1 ft to 300 ft transmission range, 100 steps • Receive signal strength detector

Network Programming and Storage • ATMEGA103 in-circuit, but external reprogramming • retain secondary co-processor • AT90LS2343 only small device with internal clock and in-circuit programming • 4 Mbit flash (AT45DB041B) • Store code images, Sensor Readings and Calibration tables • 16x increase in prog. mem too large for EEPROM solution • forced to use FLASH option

Power • Incorporated On-board Voltage Regulation • Boost Converter provides stable 3V supply • Stabilizes RF performance • Allows variety of power sources • Can run on batteries down to 1.1 V • Incorporated power supply sensor • Can measure battery health • used to adjust wake-up threshold for unregulated design

Expansion Capabilities • Backwards compatible to existing sensor boards • added two analog compare lines • added five interrupt lines • added two PWM lines • Can connect external SRAM for CPU data memory (up to 64KB) • lose most sensor capability • address lines share with lowest priority devices (LEDS, Flash ctrl) • still allows radio, flash, and programming

Why Not Faster/Different Radio? • RFM TR1000 is the lowest power RF Transceiver on the market • Simplistic design leads to rapid power cycling • High speed radios usually come with digital protocol logic forcing users into set communication regimes • Raw interface to the RF transmission allows for exploration of new communication paradigms (Proximity Mode and Sleep)

Outline • Previous designs and factors motivating new design • Mica Architecture and Hardware Details • Architectural Implications (RADIO, CPU interface) • Performance characteristics in key areas • Future directions

Wireless Communication Phases Transmit command provides data and starts MAC protocol. … Transmission … Data to be Transmitted … Encode processing … Encoded data to be Transmitted Start Symbol Transmission … MAC Delay Transmitting encoded bits Bit Modulations … Radio Samples Start Symbol Search Receiving individual bits Synchronization … Reception Start Symbol Detection Encoded data received Decode processing Data Received

Radio Interface • Highly CPU intensive • CPU limited, not RF limited in low power systems • Example implementations • RENE node: • 19,200 bps RF capability • 10,000 bps implementation, 4Mhz Atmel AVR • Chipcon application note example: • 9,600 bps RF capability • Example implementation 1,200bps with 8x over sampling on 16 Mhz Microchip PICmicro (chipcon application note AN008)

Why not use dedicated CPU? • Dedicated communications processor could greatly reduce protocol stack overhead and complexity • Providing physical parallelism would create a partition between applications and communication protocols • Isolating applications from protocols can prove costly Flexibility is Key to success

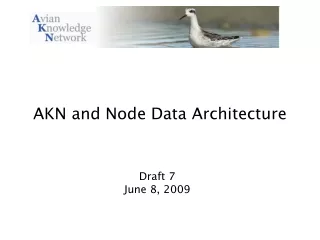

Classic Protocol Processor Direct Device Control Application Controller Application Controller Narrow, refined Chip-to-Chip Interface Protocol Processor RF Transceiver Raw RF Interface RF Transceiver Hybrid Accelerator Application Controller Memory I/O BUS Hardware Accelerators Serialization Accelerator Timing Accelerator RF Transceiver Node Communication Architecture Options

Accelerator Approach • Standard Interrupt based I/O perform start symbol detection • Timing accelerator employed to capture precise transmission timing • Edge capture performed to +/- 1/4 us • Timing information fed into data serializer • Exact bit timing performed without using data path • CPU handles data byte-by-byte

Results from accelerator approach • Bit Clocking Accelerator • 50 Kbps transmission rate • 5x over Rene implementaiton • >8x reduction in CPU overhead • Timing Accelerator • Edge captured to +/- ¼ us • Rene implementation = +/- 50 us • CPU data path not involved

Outline • Previous designs and factors motivating new design • Mica Architecture and Hardware Details • Architectural Implications (RADIO, CPU interface) • Performance characteristics in key areas • Future directions

Incremental Improvement • ATMEGA128 • Self Reprogrammable • Hardware Multiplier • JTAG debugging support: real-time, in-system debugging • Chipcon CC1000 radio • Programmable transmission frequency • Automatic bit timing • 2.3V operation voltage

The Leap • MOTE on a chip • Integration of radio, CPU, protocol accelerators onto a single silicon die. • Investigate set of hardware accelerators customized to the needs of sensor networks • Start Symbol Detection • Bit timing • Bit correlation • Channel encoding • Low power channel monitoring • Optimal communication timing