Conversion from one number base to another Equation simplification Conversion to/from SOP/POS

450 likes | 687 Vues

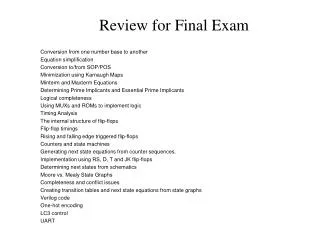

Review for Final Exam. Conversion from one number base to another Equation simplification Conversion to/from SOP/POS Minimization using Karnaugh Maps Minterm and Maxterm Equations Determining Prime Implicants and Essential Prime Implicants Logical completeness

Conversion from one number base to another Equation simplification Conversion to/from SOP/POS

E N D

Presentation Transcript

Review for Final Exam Conversion from one number base to another Equation simplification Conversion to/from SOP/POS Minimization using Karnaugh Maps Minterm and Maxterm Equations Determining Prime Implicants and Essential Prime Implicants Logical completeness Using MUXs and ROMs to implement logic Timing Analysis The internal structure of flip-flops Flip-flop timings Rising and falling edge triggered flip-flops Counters and state machines Generating next state equations from counter sequences. Implementation using RS, D, T and JK flip-flops Determining next states from schematics Moore vs. Mealy State Graphs Completeness and conflict issues Creating transition tables and next state equations from state graphs Verilog code One-hot encoding LC3 control UART

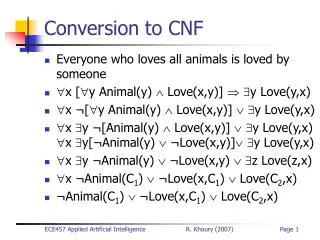

Equation simplification X + XY = X X + X’Y = X + Y X + XY = X (X + Y)(X + Z) = (X + YZ)

Conversion to/from SOP/POS (X + YZ) = (X + Y)(X + Z)

Minimization using Karnaugh Maps AB + C’D + A’B’C + ABCD + AB’C AB + C’D + B’C

Minterm and Maxterm Equations F(ABCD) = Sm (0,2,4,7,9,12,14,15) BC’D’ + BCD + ABC + A’B’D’ + AB’C’D

Determining Prime Implicants and Essential Prime Implicants 6 prime implicants 3 essential prime implicants

Logical completeness Inverter Inverter AND gate NAND Inverter Inverter OR gate AND gate Inverter

0 forAB=00, Z=0 Implementing Logic Functions With Muxes Implement: Z = A’B + BC’ I0 I1 I2 I3 4-to-1 MUX Z A B

1 forAB=01, Z=1 Implementing Logic Functions With Muxes Implement: Z = A’B + BC’ I0 I1 I2 I3 0 4-to-1 MUX Z A B

C’ forAB=11, Z=C’ Implementing Logic Functions With Muxes Implement: Z = A’B + BC’ I0 I1 I2 I3 0 1 4-to-1 MUX Z A B

Implementing Logic Functions With Muxes Implement: Z = A’B + BC’ I0 I1 I2 I3 0 1 4-to-1 MUX Z 0 C’ A B

Implementing Logic Functions With Muxes An alternate method Z = A’B + BC’ Z = 1 0 + 0 C’ = 0 A=0 B=0 A=0 B=1 A=1 B=0 A=1 B=1 I0 I1 I2 I3 0 Z = 1 1 + 1 C’ = 1 1 4-to-1 MUX Z 0 Z = 0 0 + 0 C’ = 0 C’ Z = 0 1 + 1 C’ = C’ A B

Using a ROM For Logic Specify a truth table for a ROM which implements: F = AB + A’BC’ G = A’B’C + C’ H = AB’C’ + ABC’ + A’B’C

Using a ROM For Logic Specify a truth table for a ROM which implements: F = AB + A’BC’ G = A’B’C + C’ H = AB’C’ + ABC’ + A’B’C

Using a ROM For Logic Specify a truth table for a ROM which implements: F = AB + A’BC’ G = A’B’C + C’ H = AB’C’ + ABC’ + A’B’C

D R D GR Q Q’ Q S Q’ Q Q’ GS GATE GATE CLK The internal structure of flip-flops D-type Flip-Flop

Q T Q’ CLK The internal structure of flip-flops T-type Flip-Flop

The internal structure of flip-flops J Q Q’ K CLK JK-type Flip-Flop

Flip-flop timingsClock-to-Q D Q Q’ CLK tCLK ! Q = tNOT + tAND + 2 x tNOR

Flip-flop timingsSetup time D Q Q’ CLK tsetup = tNOT + tAND + 2 x tNOR

Flip-flop timingsHold time D Q Q’ thold = tNOT CLK

Flip Flop Timing thold tsetup CLK D Q tCLK ! Q time

Rising and falling edge triggered flip-flops D Q Q’ CLK Falling Edge Triggered DFF

Rising Edge Triggered DFF Rising and falling edge triggered flip-flops D Q Q’ CLK

N2 = Q2 Q1’ + Q1’ Q0 N1 = Q2 N0 = Q2’ Q0’ + Q1 Q0’ Generating next state equations from counter sequences. Desired count sequence = 00 01 00 10 11 00 … If current state = 00, next state = ????? Implemented count sequence = 000 001 100 110 011 000 …

D Q D Q D Q Determining next states from schematics Q2 Q2 Q1 Q0 0 0 0 0 0 1 1 0 0 1 1 0 Q1’ Q2 Q1’ Initial state Q0 CLK Q1 Q2 CLK Q2’ Q0’ Q0 Q1 Q0’ CLK

For general purpose FSMs, the encoding of the states is usually not significant For example, in the following state graph, the Encodings of the state are irrelevant Event 2 … Event 1 Event 1 Event 2 Event 3

Completeness Issues • In order for a state graph to be complete: • It must completely specify the FSM • Paths leaving a state must specify all POSSIBLE cases • To check for completeness, OR together all of the exiting paths. • If the result is “1” then the design is complete.

Conflict Issues • In order for a state graph to be conflict free: • It must completely specify the FSM • For a given set of input conditions, the transition • from a state must be unique • To check for conflicts, AND together all pairs of the exiting paths. If the result is “0” for all pairs, the design has no conflicting transitions.

Creating transition tables and next state equations from state graphs

The resulting next state and output equations are: N1 = Q0 + Q1 TDONE’ N0 = TOKEN Q1’ Q0’ CLRT = Q0 SPRAY = Q1

B A PC ALU IR

LC-3 Instructions ADD LD DR DR SR1 SR2 0001 00 0 0010 PCoffset9 ADD LDI DR imm5 1010 PCoffset9 0001 DR SR1 1 AND LDR DR DR SR1 SR2 0101 BaseR 00 0 0110 offset6 DR AND LEA imm5 0101 DR SR1 1 1110 PCoffset9 NOT DR SR SR 1001 111111 ST PCoffset9 0011 STI BR p z 0000 n PCoffset9 SR PCoffset9 1011 JMP STR SR BaseR 1100 0 00 000000 0111 BaseR offset6 JSR TRAP PCoffset11 0100 1 1111 0000 trapvect8 JSRR RTI BaseR 0100 0 00 000000 1000 000000000000 reserved RET 111 1100 0 00 000000 1101