VHDL and Hardware Tools

VHDL and Hardware Tools. CS 184, Spring 4/6/5. Hardware Design for Architecture. What goes into the hardware level of architecture design? Evaluate design alternatives: Area requirements Operation latencies Complementary to: Architecture language design Compiler design Benchmark design.

VHDL and Hardware Tools

E N D

Presentation Transcript

VHDL and Hardware Tools CS 184, Spring 4/6/5

Hardware Design for Architecture • What goes into the hardware level of architecture design? • Evaluate design alternatives: • Area requirements • Operation latencies • Complementary to: • Architecture language design • Compiler design • Benchmark design

Why VHDL • VHDL and Verilog are the best supported hardware languages. • We are more familiar with VHDL

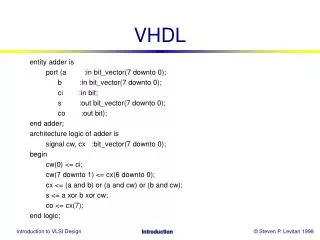

What is VHDL • Slightly higher level than Register Transfer Language (RTL) • RTL describes a graph of logic gates and registers. • C : MIPS :: VHDL : RTL • Nicer syntax • Stylized control flow • Packaging, abstract interface from implementation • Access to lower level semantics • C - MIPS > VHDL - RTL • Mostly think in RTL when I code VHDL • Some scheduling for C -> MIPS (Register scheduling) • Both expose cycle precise timing of data flow • Though compiler can retime registers

VHDL Example • mem_accum semantics • Data paths (unregistered) • RESET, CLK • States: writing, sum_start, summing • Register outputs to pipeline • Initialize registers on sum_start • Time correctly • Mop up: signal declarations, resets

VHDL Example • LUTram inference • Control structures • If then else • Case • Data types • boolean: pass to control structures • std_logic: single bit • std_logic_vector • number: constants, memory addresses, arith args

VHDL Example • Bind generics to constants to simulate and compile • mem_accum_2_16

Compilation Example • ise is Integrated Development Environment for Xilinx devices. • Synplify Pro (synplify_pro) syntax checks • Log file: mem_accum_2_16.srr • Model Sim (vsim) simulates • Stimulator script: mem_accum.vsim • Synplify Pro performs synthesis • Xilinx tools perform rest of compilation