Triplet Finder

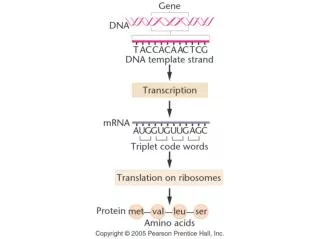

Triplet Finder. Jinyuan Wu Dec. 2003. Triplets. Bit Arrays. Triplet Finding (1) Filling Bit Arrays. Note: Flipped Bit Order. Physical Planes. Fill a corresponding logic cell. For any hit…. Bit Arrays. Triplet Finding (2) Looping, Shifting and Matching. Triplet is found.

Triplet Finder

E N D

Presentation Transcript

Triplet Finder Jinyuan Wu Dec. 2003

Bit Arrays Triplet Finding (1) Filling Bit Arrays Note: Flipped Bit Order Physical Planes Fill a corresponding logic cell. For any hit…

Bit Arrays Triplet Finding (2) Looping, Shifting and Matching Triplet is found. Logically shift the bit array. Bit-wise AND in this range. Physical Planes For any center plane hit…

Bit Arrays Triplet Finding (2) Looping, Shifting and Matching Triplet is found. Fake triplet will be cut out in the later stages. Physical Planes

Bit Arrays Triplet Finding (2) Looping, Shifting and Matching Physical Planes

Bit Arrays Triplet Finding (2) Looping, Shifting and Matching Physical Planes

Bit Arrays Triplet Finding (2) Looping, Shifting and Matching Physical Planes

D D D D D D D D Q Q Q Q Q Q Q Q WE WE WE WE WE WE WE WE A(3:0) A(3:0) A(3:0) A(3:0) A(3:0) A(3:0) A(3:0) A(3:0) Bit Array/shifterXILINX Implementation • Each Bit Array/Shifter has 64 bins. • Each bin is a 16-bit RAM (look-up table). • The RAM operates like a D Flip-flop. • Each xc2v1000 FPGA has 10,240 such RAM’s.

Bit Array/shifterFilling the Hits • Each hit is written into 8 to 16 different RAM’s with different addresses. • One clock cycle (not 8 to 16) is used to fill a hit.

Bit Array/shifterShift Reading • With given addresses of the RAM’s, hit patterns appear at the outputs of the arrays. • Changing addresses shifts the hit patterns. • One array shifts in unit of 1 bin, the other in unit of 8 bins. • The relative shift of the two patterns covers 128 bins. • One clock cycle is used for a reading, regardless the distance of the relative shifting.

D D D D D D D D Q Q Q Q Q Q Q Q WE WE WE WE WE WE WE WE A(3:0) A(3:0) A(3:0) A(3:0) A(3:0) A(3:0) A(3:0) A(3:0) Bit Array/shifterComments • Writing/reading operations need only single clock cycle. • Storage and shifter are combined — big resource saving. • Maximum 16 clock cycles are needed for resetting. • Non-xilinx implementation: Additional 64x8=512 LE’s may be needed. But resetting is a single clock one.

Multiple Hits, TripletsKeep Them All • Each bin may be filled with more than one hits. • Hits data are kept in hash sorters – allowing multiple hits per bin. • There are may be more than one matches in each bit-wise AND operation. • They are all sent out, one-by-one, to the later stages for fine cut and arbitration processes.

FIFO Interface Hit Feeder C FIFO Interface Hit Feeder A Hash2blk Hash2blk D D QC QA DI DI QQ QQ K K KA KC Push Push RDY RDY EN EN Push Push Pop Pop WT WT RePop RePop MD MD SR SR Bit64A Bit64C KS KS WR WR Q Q EN EN SR SR FIFO Interface Hit Feeder B D SA Cut and Arbitration DA QB DB QT EN XB DC RDY SC EN Chk Shift Reg. 6 steps D Q4 EN 77 LUT 66 FF DA 172 LUT FF 192 LUT 111 FF 92 LUT FF A BitLogic KA XB C KC EN Pop 77 LUT 66 FF Halt

CB10E RAM 512x18 RAM 256x36 Q D D O O CE D D O O WE WE EN EN A A A3 A2 COMP A A1 A1 EQ A0 B S0,S1 A0 S0 CB8RE Q CE FD FD FD FD FD FD D D Q Q D Q D Q D D Q Q SR EN EN EN POP POPQ RDY REPOP WT EVeq MD EV(9:0) IdK(7:0) IdKQ(7:0) EV(8:0) K(8:0) DOB(27:0) DI(27:0) DIQ(27:0) IdN(7:0) PUSH PUSHQ DUMPD IdP(7:0) IdQ(7:0) SR Vertex II Implementation CLK

CB9E RAM 256x16 RAM 128x36 Q D D O O CE D D O O WE WE EN EN A A A3 A2 COMP A A1 A1 EQ A0 B S0,S1 A0 S0 CB7RE Q CE FD FD FD FD FD FD D D Q Q D Q D Q D D Q Q SR EN EN EN POP POPQ RDY REPOP WT EVeq MD EV(8:0) IdK(6:0) IdKQ(6:0) EV(7:0) K(7:0) DOB(28:0) DI(28:0) DIQ(28:0) IdN(6:0) PUSH PUSHQ DUMPD IdP(6:0) IdQ(6:0) SR Cyclone Implementation CLK

The End Thanks

RAM D CC8RLE Q D O L WE EN CE SR A CB8SE S1 SS RAM CE D O Q FD FD D D Q Q D O CE CE WE EN A A0 A1 A2 A3 S NBin DOB DI IdNext