The Emerging Electronic Design Automation

370 likes | 517 Vues

The Emerging Electronic Design Automation. Design Technology Needs for Supporting Emerging Reaches of Silicon Rajesh Gupta, UC San Diego gupta@ucsd.edu. http://www.cse.ucsd.edu/~gupta. A Chip Is A Wonderful Thing!. A typical chip, circa: 2006 50 square millimeters 50 million transistors

The Emerging Electronic Design Automation

E N D

Presentation Transcript

The Emerging Electronic Design Automation Design Technology Needs for Supporting Emerging Reaches of Silicon Rajesh Gupta, UC San Diego gupta@ucsd.edu http://www.cse.ucsd.edu/~gupta

A Chip Is A Wonderful Thing! A typical chip, circa: 2006 • 50 square millimeters • 50 million transistors • 1-10 GHz, 100-1000 MOP/sq mm, 10-100 MIPS/mW • 300 mm, 10,000 units/wafer, 20K wafers/month • $5 per part Does not matter what you build • Processor, MEMS, Networking, Wireless, Memory • So there is a strong incentive to port your application, system, box to the “chip”

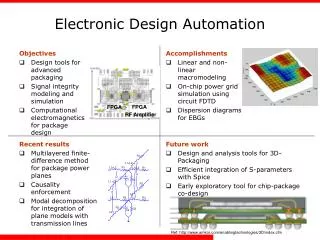

Systems Tools Mask data Components Masks Source: IBS 2003 The Technology and Its Industry

The EDA Industry • Current EDA market • $1B Synthesis and verification • $400M synthesis, $400M verification, $200M Emulation • $2.7in PDA, IP and Design Services. • 8% Y-Y growth in Q2/2003 • More like 6.0% for tool licenses (85% of revenue) • Revenue Drivers for EDA • Semiconductor R&D spending • Design completion activity • Semiconductor capital expenditures (backend EDA tools) • Good chips and more chips lead to EDA growth

But it costs $20M to build one… Source: IBS 2003 • Not a problem, until you consider this…

“Disaggregation” in Semis • Of the 72 distinct application markets that rely on value added IC designs (ASIC, ASSP, FPGA, SOC) • over 50% are less than $500M • 75% are less than $1B • Manufacturing is no longer a competitive advantage Source: IBS

Rising Fabless, Fablite • Currently at $20B • about 15% of the semiconductor market • going up to 50% by 2006 • Design technology needs are not the same as those of high value part manufacturers • Example: Baseband and CMOS Radio Source: Teresa Meng, Atheros

A Changing Industry • Structural Changes • Outsourcing: Fabrication, Design Implementation • Technological Changes • New materials and devices being explored to overcome the roadmap “brickwalls” • The mega-investments into nanotechnology • History tells us that fundamental device discoveries happen within a relatively short period of time • All major components of IC today were invented within a 10-year period from the Shockley transistor in 1947 • But a long development cycle for manufacturing (more on it later)

…Dragging EDA Along With It • (Rapidly) Falling ASIC Starts • From 10K in 1996 to about 2K in 2005 • Rise of FPGAs and Deep Deep Submicron Noise • Can lead to shrinking or at best stationary market in ICs • “EDA moving from expansion to retention phase.” • [Desai, Industry Update, Nov 2003] • More and more it is EDA consuming itself • Revenue reallocation within the same block: Verification, Synthesis • Major portions of EDA revenues are business with itself • Basic value proposition is being lost • OTOH, Dataquest predicts 15% growth based on ESL expansion • The record there is not so good so far • Compilers, embedded systems, software • Embedded software is about a $1B • Are we becoming irrelevant?

What Must EDA Do? A Three-Point Prescription: • Understand the new silicon • Enable box makers expand reach of silicon • Understand that marketplace is not everything

1 The New Semi Characteristics • Highly application specific • domain specific IC design, focus on system level • Content increasingly determines processing • “embedded intelligence” through embedded software • Connection more important than processing • bandwidth delivery more important than computational efficiency

1 New Semi Challenges • Need streamlined/simplified system architectures • gain from scalability, adaptability, not from design complexity • The technology favors concurrency than speed • Design reuse, design closure and sign-off • make IP viable through software value add and platform ownership • Key technical challenges • Productivity, Power, Heterogeneous Integration, Test • Getting it right means many more systems capabilities through Software

1 Design Decisions Are Important Source: Teresa Meng

1 And Likelihood of Failure High

1 Engineering Moving Up • Chip Engineering Moving Up and Moving Down • Systems Engineering versus Silicon Engineering • Silicon Engineering Hot-buttons • Design for Manufacturing • Defect-tolerant Design • EDA has been so far supporting Silicon Engineering • With lip-service to System Engineering

1 Systems Engineering Example Problem: How to achieve high throughput in a SOC for wireless applications? • Can select a modem sub-system • that packs more bits/Hz, but it will tolerate less noise and be less robust so that link throughput may not improve • Can increase transmit power in RF subsystem • to improve robustness but this increases energy cost, reduces network capacity, and requires more expensive analog circuits (power amps) • Can reduce bits/frame • to tolerate higher bit error rates (BER) and provide more robustness, but this may increase overhead and queuing delays • Can increase precision in digital modem • to reduce noise, but this leads to wider on-chip busses and more power consumption • Getting it right (within engineering constraints) is the task of “Systems Engineering”

2 Expanding Semiconductor Use

Instrumented wide-area spaces Internet end-points In-body, in-cell, in-vitro spaces Personal area spaces 2 Future Silicon Proliferation • From Computers, Communications to • Gaming, Robotics, Biomedical, … • Going Forward Si Has Place in Major Human Endeavors • Communications: Wireless, Sensor networks, open spectrum • Entertainment: Virtual worlds, education, multimedia delivery • Medicine and Biology: lab-on-chip, devices & disability assists • Transportation: automotive, avionics • Physical Sciences: big science, life sciences • Exploration: space, oceanic

2 Accelerating Proliferation Near Future: < 5 years Going Forward: > 5 years

2 Environmental Monitoring • Santa Margarita Ecological Reserve, SMER • 4,334 acre field station 50 miles NE of San Diego with variety of habitat, terrain • A testbed for 56 ongoing experiments including sensing • Hydrology (stream flow, temp, pH, O2, conductivity..) • Microclimate, fire hazard • Chemical, biological agents • High Performance Wireless Research and Education Network • 45 Mbps wireless backbone running across southern CA connecting • SMER, Mt. Palomar, IGPP/SIO seismic network • Real-time environmental monitoring • Seismic, oceanographic, hydrological, ecological data • http://hpwren.ucsd.edu

2 Santa Margarita Ecological Reserve Water Chemistry Quality Stations Source, Dan Cayan, UCSD SIO

2 Drive Integration: BioChem Labs. • Crisis detection, evolutionary monitoring, genotyping • Computation+Networking+Sensing • In-package integration of microfluidic, communications, networking and processing subsystems • Remotely operated, reconfigurable laboratories for biochemical analysis • Sub-systems • Biofluidic sample preparation, transport, disposal • Chemical analysis, biological assays • In-situ monitoring, control, communication, adaptation

IC-like microfluidic processors for handling complex biofluids & self-calibration (BioFlips) • Micropumps, flow sensors, viscosity sensors, diffusion assayes, laminar flow-based target extractors, flow cytometers. 2 Going Forward…On-Chip Chemistry

2 Drive IC Into Fabrics and Buildings Ember radios and networks Source: Ember Networks

1 Systems Engineering through EDA Consider “Wireless SOC” • Platforms: OMAP, PCA, MXC • Basic theme: • Merging hardware: Heterogenous MP on-chip • Separating software • Communications, networking, applications • In the process, a lot of legacy stuff is left in as “overheads” • Multiple UI functions, fragmented memory system and shared memory processor locks 2

1 Multiple Heterogenous On-Chip 2 • Software development is a challenge with evolving processors • Shared memory processing • Use OS and API support to provide a “usable” programming model • Divergent approaches • TI: Integrate DSP, single programming environment • Intel, Motorola: Separate Comm, Networking, App. • What is the right programming model for these systems?

1 ESL Technology Needs • These are needs that will turn technology capacity afforded by new chips into new systems capabilities • Components and Compositional Correctness • A posteriori validation is simply not possible • Software and Software Infrastructure • Hardware capabilities and constraints driving need for new software architecture • New “awareness” into software infrastructure • Energy, Location, Reactivity, Precision, Security 2

1 1 Compositional Correctness • Build “Complete” System Models • That includes the application and system software • Adapt, control and debug applications • Explore the full potential of SOC architectural platforms • e.g., by exploring applications, networking and communication subsystems together • How? Through “Component Composition Framework” (CCF) • Define compositional semantics • enable easy system construction and its “formal” validation • “adequate”, hierarchical and verifiable composition • Create “Virtual” System Architectures • Leverage advances in programming languages and verification. 2

1 2 Software and Its Infrastructure • Changes in structure of system software • OS moving towards micro-kernels • Services moved to processes (e.g., Nucleus, Symbian) • Still legacy remains: memory, file semantics as unifying theme for communications. • Changes in division of labor among • Application, middleware, operating system • Compiler, runtime • Challenges in bringing new capabilities and contract into the system software 2

1 Consider Energy “Awareness” • What does it mean to be aware? • Services “know” about energy, power • File system, memory management, process scheduling • Make each of them energy aware • How does one make software to be “aware”? • Use “reflectivity” in software to build adaptive software • Ability to reason about and act upon itself (OS, MW) • Make middleware adaptive to respond to application requirements • and to dynamically smooth the imbalances between demand and availability of energy resource 2

What Must EDA Do? A Three-Point Prescription: • Understand the new silicon • Enable box makers expand reach of silicon • Understand that marketplace is not everything

3 EDA Technology and Marketplace • By and large EDA technology moves through startups and acquisitions • One of the few industries where the business plans do not always call for sustainable standalone business • The driver for EDA industry growth is Semiconductor R&D • Major semi innovations happened in the industry labs.

3 Semi. R&D Is Changing Rapidly • Shrinking, vanishing industry research laboratories • Industry resorting to consortia to carry out needed technology innovations and developments • Often with substantial government support • SEMATECH, SELETE, ASET, MEDIA, ITRI, HsinChuPark,…

Sematech Experience & EDATech • US Semiconductor industry gradually lost share starting late 70’s • By 1985, it lost leadership. Semi equipment vendors were loosing share about 5% per year • Its fate was pretty much sealed until the industry and Reagan administration decided to do something about “The Rising Sun” • The industry worked hard to define a “precompetitive space” • Supported the supplier industry to semi houses • $100M per year, for 8 years until 1994 • $800M investment by the government, $100M per year • By 1994, the industry assumed its leadership position.

Summary • The new Silicon comes out of the fab fast and furious • Our ability to implement and manufacture vastly exceeds our capability to architect, reason and validate the new generation of silicon systems • Our challenge is to make sure what goes into manufacturing has tremendous value-add to end application (systems) • Software is the defining IP • But it is a whole new ballgame: new awareness, fangled, adaptive, … • R&D leadership necessary to turn Si advantage into new systems capabilities • New applications as reflected in new forms of computing • Cognitive, Mobile, Entertainment, Embedded, Wireless, Trusted/secure computing, and so on. • If left alone, the gap between our systems capabilities and new Si possibilities will continue to widen.

Questions to ponder • What is the right precompetitive space for EDA? • Frameworks • Backend backplane • Data format standards • Language, libraries, models, models of computation • What is the next big application space for Semis? • Lab-on-chip, smart fabrics, appliances, robotics • What are the training needs for the EDA professional? And where will the jobs be? • Systems engineering, Nanotechnology, Biology, Chemistry • What is “Plan B” for EDA? • How can EDA expand beyond supplier to Semis?