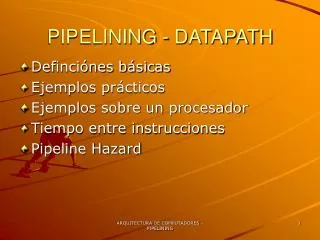

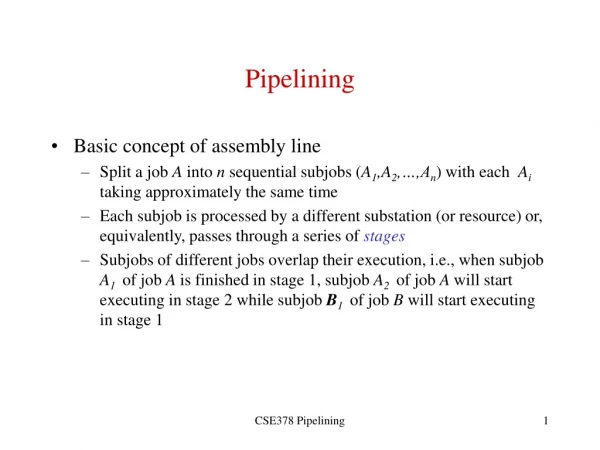

PIPELINING - DATAPATH

PIPELINING - DATAPATH. Definciónes básicas Ejemplos prácticos Ejemplos sobre un procesador Tiempo entre instrucciones Pipeline Hazard. SINGLE –CYCLE DATAPATH.

PIPELINING - DATAPATH

E N D

Presentation Transcript

PIPELINING - DATAPATH • Definciónes básicas • Ejemplos prácticos • Ejemplos sobre un procesador • Tiempo entre instrucciones • Pipeline Hazard ARQUITECTURA DE COMPUTADORES - PIPELINING

SINGLE –CYCLE DATAPATH Figure 6.9 The single-cycle datapath from chapter 5 (similar to figure 5.17 on page 307). Computer Organization and Design. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

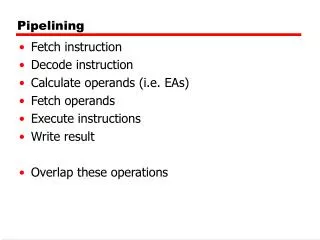

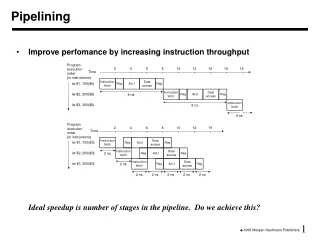

PIPELINED EXECUTION Figure 6.10 Instruction being executed using the single cycle datapath in figure 6.9 . Computer Organization and Design. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

THE PIPELINED VERSION Figure 6.11 The Pipelined version of the datapath in figure 6.9. Computer Organization and Design. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

EJEMPLO • EL siguiente ejemplo sigue el proceso de pipelining para una instrucción LOAD ARQUITECTURA DE COMPUTADORES - PIPELINING

INSTRUCTION FETCH • La instrucción es leida de memoria, de la dirección apuntada por PC • La instrucción es almacenada en el IF/ID pipelined register. • PC=PC+4. • Aquí no se sabe que instrucción se va a ejecutar. ARQUITECTURA DE COMPUTADORES - PIPELINING

FETCH Figure 6.12 IF and ID: first and secod stages of an instruction. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

INSTRUCTION DECODE AND REGISTER FILE READ • Se obtiene • 16 bit inmediate field, que es el dato de entrada para sign-extend (32 bit) • Dirección (número) de registro a ser leído. • Todos los valores se almacenan en ID/Ex pipeline register ARQUITECTURA DE COMPUTADORES - PIPELINING

INSTRUCTION DECODE –REGISTER FILE READ Figure 6.12 IF and ID: first and secod stages of an instruction. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

EXECUTE OR ADDRESS CALCULATION • Para el ejemplo se muestra que la instrucción LOAD toma: • El contenido del register 1 y del sign extend y los asigna a la ALU. • El resultado es almacenado en EX/MEN pipeline register ARQUITECTURA DE COMPUTADORES - PIPELINING

EXECUTION Figure 6.13 EX: the third pipe stage of a load instruction. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

MEMORY ACCESS • Se lee el dato de la memoria empleando la dirección almacenada en EX/MEM pipeline register. • Se almacena en el MEM/WB pipeline register. ARQUITECTURA DE COMPUTADORES - PIPELINING

MEMORY ACCESS Figure 6.14MEM and WB: the fourth and fith pipe stages of a load instruction. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

WRITE BACK • Se lee el valor del dato del registro MEM/WB pipeline register • Se almacena en el register file ARQUITECTURA DE COMPUTADORES - PIPELINING

WRITE BACK Figure 6.14 MEM and WB: the fourth and fith pipe stages of a load instruction. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

EJEMPLO PARA UNA INSTRUCCIÓN STORE • EXECUTE: Para una instrucción STORE debe dejar pasar en la ALU read register 2 • MEMORY ACCESS: Se realiza memory write • WRITE BACK: en una instruction STORE en este estado no sucede nada ARQUITECTURA DE COMPUTADORES - PIPELINING

EXECUTION STAGE Figure 6.15 EX: the third pipe stage of a store instruction. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

MEMORY ACCESS Figure 6.16 MEM AND WB: the fourth and fifth pipe stage os a store instruction. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

DIAGRAMA COMPLETO Figure 6.17 The corrected pipelined datapath to properly handle the load instrction. David A Paterson ARQUITECTURA DE COMPUTADORES - PIPELINING

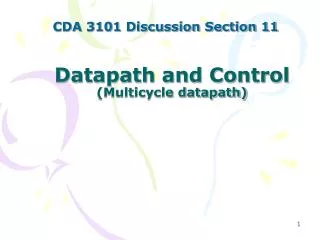

MULTICYCLE ARQUITECTURA DE COMPUTADORES - PIPELINING

EJEMPLOS ARQUITECTURA DE COMPUTADORES - PIPELINING