Binary Arithmetic Operations in Multipliers and Dividers

This presentation covers various binary arithmetic operations, including multiplication and division techniques used in digital circuits. Explore different algorithms and illustrated examples for better understanding.

Binary Arithmetic Operations in Multipliers and Dividers

E N D

Presentation Transcript

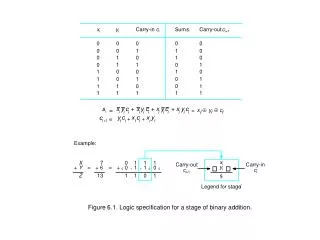

x y Carry-in c Sum s Carry-out c i i i i i +1 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 x y c + x y c + x y c + x y c s = = x Å y Å c i i i i i i i i i i i i i i i i y c x c x y c = + + i i i i i i i +1 E xample: x X 7 0 1 1 1 Carry-out Carry-in i y + Y = + 6 = + 0 1 1 0 0 1 1 0 0 c i c i +1 i Z 13 1 1 0 1 s i Legend for stage i Figure 6.1.Logic specification for a stage of binary addition.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.2. Logic for addition of binary vectors.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.4. 4-bit carry-lookahead adder.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.6. Array multiplication of positive binary operands.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.7. Sequential circuit binary multiplier.

1 0 0 1 1 ( - 13 ) ( ) ´ 0 1 0 1 1 + 11 1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 0 0 1 1 Sign extension is 0 0 0 0 0 0 0 0 shown in blue 1 1 1 0 0 1 1 0 0 0 0 0 0 1 1 0 1 1 1 0 0 0 1 ( - 143 ) Figure 6.8.Sign extension of negative multiplicand.

0 1 0 1 1 0 1 0 0 + 1 + 1 + 1 + 1 0 0 0 0 0 0 0 0 0 1 0 1 1 0 1 0 1 0 1 1 0 1 0 1 0 1 1 0 1 0 1 0 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 1 1 0 0 1 0 1 1 0 1 + 1 - 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 2's complement of 1 1 1 1 1 1 1 0 1 0 0 1 1 the multiplicand 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 1 1 0 Figure 6.9.Normal and Booth multiplication schemes.

0 0 1 0 1 1 0 0 1 1 1 0 1 0 1 1 0 0 0 0 0 0 0 0 0 0 + 1 - 1 + 1 - 1 + 1 - 1 + 1 - 1 + 1 - 1 Figure 6.10.Booth recoding of a multiplier.

0 1 1 0 1 ( + 13 ) 0 1 1 0 1 1 1 0 1 0 0 - 1 +1 - 1 0 ´ ( - 6 ) 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 1 1 0 0 0 0 1 1 0 1 1 1 1 0 0 1 1 0 0 0 0 0 0 1 1 1 0 1 1 0 0 1 0 ( - 78 ) Figure 6.11.Booth multiplication with a negative multiplier.

Multiplier V ersion of multiplicand selected by bit i i - Bit i Bit 1 0 0 0 ´ M 0 1 + 1 ´ M 1 0 1 ´ M 1 1 0 ´ M Figure 6.12.Booth multiplier recoding table.

0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Worst-case multiplier + 1 - 1 + 1 - 1 + 1 - 1 + 1 - 1 + 1 - 1 + 1 - 1 + 1 - 1 + 1 - 1 1 1 0 0 0 1 0 1 1 0 1 1 1 1 0 0 Ordinary multiplier 0 - 1 0 0 + 1 - 1 + 1 0 - 1 + 1 0 0 0 - 1 0 0 0 0 0 0 1 1 1 1 1 0 0 0 0 1 1 1 Good multiplier 0 0 0 + 1 0 0 0 0 - 1 0 0 0 + 1 0 0 - 1 Figure 6.13.Booth recoded multipliers.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.14. Multiplier bit-pair recoding.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.15. Multiplication requiring only n/2 summands.

Figure 6.16. Ripple-carry and carry-save arrays for the multiplication operation M Q = P for 4-bit operands.

(45) M 1 0 1 1 0 1 (63) Q 1 1 1 1 1 1 X A 1 0 1 1 0 1 B 1 0 1 1 0 1 C 1 0 1 1 0 1 D 1 0 1 1 0 1 E 1 0 1 1 0 1 F 1 0 1 1 0 1 (2,835) Product 1 0 1 1 0 0 0 1 0 0 1 1 Figure 6.17. A multiplication example used to illustrate carry-save addition as shown in Figure 6.18.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.18. The multiplication example from Figure 6.17 performed usingcarry-save addition.

Figure 6.19. Schematic representation of the carry-save addition operations in Figure 6.18.

1101 13 21 10101 274 100010010 26 1101 14 10000 13 1101 1 1110 1101 1 Figure 6.20. Longhand division examples.

Shift left a a a q q n n - 1 0 n - 1 0 A Dividend Q Quotient setting Add/Subtract n + 1 -bit adder Control sequencer m m 0 n - 1 0 Divisor M Figure 6.21.Circuit arrangement for binary division.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.22. A restoring-division example.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.23. A nonrestoring-division example.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.24. IEEE standard floating-point formats.

excess-127 exponent 1 0 0 0 1 0 0 0 0 0 1 0 1 1 0 ... 0 (There is no implicit 1 to the left of the binary point.) 9 Value represented = + 0.0010110 ¼ ´ 2 (a) Unnormalized value 0 1 0 0 0 0 1 0 1 0 1 1 0 ... 6 Value represented = + 1.0110 ¼ ´ 2 (b) Normalized version Figure 6.25.Floating-point normalization in IEEE single-precision format.

Please see “portrait orientation” PowerPoint file for Chapter 6 Figure 6.26. Floating-point addition-subtraction unit.

Representation Examples +526 - 526 +70 - 70 Sign and magnitude 9' s complement 0526 9473 0070 9929 10' s complement 0526 9474 0070 9930 Figure P6.1. Signed numbers in base 10 used in Problem 6.3.

12 bits 5 bits 6 bits 1 bit for sign of number excess-15 fractional exponent mantissa + 0 signifies 1 signifies - Figure P6.2.Floating-point format used in Problem 6.25.

(3) 0 0 1 1 (6) 0 1 1 0 - + ( 5 ) + 0 1 0 1 0 + ( - 3 ) + 1 1 1 0 0 0 1 0 0 0 1 0 0 - 2 1 1 0 1 3 0 0 1 0 0 1 1 1 0 1 0 0 1 1 Figure P6.3. 1's-complement addition used in Problem 6.36.