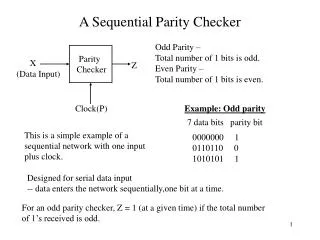

A Sequential Parity Checker

A Sequential Parity Checker. Odd Parity – Total number of 1 bits is odd. Even Parity – Total number of 1 bits is even. Parity Checker. X. Z. (Data Input). Clock(P). Example: Odd parity. 7 data bits parity bit. This is a simple example of a sequential network with one input

A Sequential Parity Checker

E N D

Presentation Transcript

A Sequential Parity Checker Odd Parity – Total number of 1 bits is odd. Even Parity – Total number of 1 bits is even. Parity Checker X Z (Data Input) Clock(P) Example: Odd parity 7 data bits parity bit This is a simple example of a sequential network with one input plus clock. 0000000 1 0110110 0 1010101 1 Designed for serial data input -- data enters the network sequentially,one bit at a time. For an odd parity checker, Z = 1 (at a given time) if the total number of 1’s received is odd.

A Sequential Parity Checker State Encoding: S0 Q = 0 S1 Q = 1 State Graph State Table for T-FF implementation State Table Timing Diagram Network

Moore Sequential Network -a sequential network whose output is a function of the present state only. X = 1 0 1 0 1 A = 0 1 1 1 1 0 B = 0 1 1 0 0 1 Z = (0) 1 1 0 0 1

Mealy Sequential Network -a sequential network whose output is a function of both the present state and the input. X = 1 0 1 0 1 A = 0 0 0 1 1 0 B = 0 1 1 1 1 0 Z = 1(0)1 0(1)0 1 A “false” value arises because the network has assumed a new state but the old input associated with the previous state is still present.

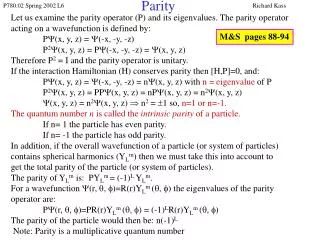

Deriving the State Table 1. Determine the FF input equations and the output equations from the network. 2. Derive the next-state equation for each FF from its input equations using the characteristic equation D FF Q+ = D T-FF Q+ = T Q SR-FF Q+ = S + R’Q JK-FF Q+ = JQ’ + K’Q 3. Plot a next state map for each FF 4. Combine these maps to form the state table.

Moore Sequential Network The FF input eqns. and output eqn. are JA = X KA = XB’ Z = B JB = X KB = X A’ The next state eqns. for the FF’s are A+ = JAA’ + K’AA = XA’ + (X’ + B)A B+ = JB B’ + K’BB = XB’ + (X A’)’B = XB’+(XA’+ X’A)B

Moore Sequential Network Moore State Graph Moore State Tables

Mealy Sequential Network The next-state and output eqns. are

Mealy Sequential Network input/output Mealy State Graph Mealy State Tables

Mealy Sequential Network -- Another Example -two inputs and two outputs

Mealy Sequential Network -- General Model D-FF’s Combinational subnetwork realizes the n output functions and the k next state functions, which serve as inputs to the D=FF’s. All FF’s change state synchronous with clock pulse. After FF’s change state the new FF outputs are fed back into the combinational subnetwork awaiting the next clock pulse.

Moore Sequential Network -- General Model D-FF’s -Similar to Mealy. In the combinational subnetwork the output section is drawn separately from the input section. (Output is only a function of the present state.)

State Table with Multiple Inputs and Outputs Let X=0 rep. the input combination X1X2= 00, X=1 rep. X1X2= 01, etc. Let Z=0 rep. the output combination Z1Z2= 00, Z=1 rep. Z1Z2= 01, etc. Obtain the following table in terms of a single input variable X and a single output variable Z. d(S0 , 1) = S2d(S2 , 3) = S1 Next State functions … S+ = d(S,X) l(S0 , 1) = 2 l(S2 , 3) = 1 Output function …….. Z = l(S,X)

What do you have to know? • Analysis of clocked sequential networks • State Graph, State Table, Network Realization • Timing Diagrams • Deriving State Table • Moore and Mealy State machines • General Models for Sequential Networks