Elektronik Devrelerin Optimizasyonu

340 likes | 836 Vues

Elektronik Devrelerin Optimizasyonu. Yrd. Doç. Dr. Revna ACAR VURAL 15.04.2014. Elektronik Devre Tasarım Problemi. Elektronik devrelerin tasarımı maddi yükümlülüğü yüksek bilimsel çalışma gerektirir. Tasarım için ayrılan zaman, yüksek sayıda eleman içeren sistemler için yıllar alabilmektedir.

Elektronik Devrelerin Optimizasyonu

E N D

Presentation Transcript

Elektronik Devrelerin Optimizasyonu Yrd. Doç. Dr. Revna ACAR VURAL 15.04.2014

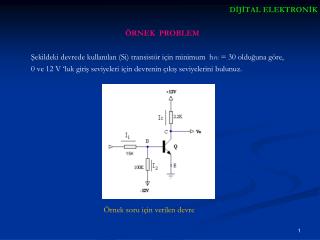

Elektronik Devre Tasarım Problemi • Elektronik devrelerin tasarımı maddi yükümlülüğü yüksek bilimsel çalışma gerektirir. • Tasarım için ayrılan zaman, yüksek sayıda eleman içeren sistemler için yıllar alabilmektedir. • Lineer olmayan sistemleri tanımlamak için kullanılan devre denklem takımları da lineer olmayacağı için ağır hesap yükü gerektirmektedir. • Her tasarımcı tasarlayacağı devrenin hangi koşullarda çalışacağına dair bir takım kriterler belirlemelidir. • Devre tasarım parametreleri ile tanımlanan bu kriterler birbiri ile çelişebilir.

Optimizasyon nedir? • Elektronik devre tasarım kalitesinin performans, güvenilirlik ve maliyet açısından iyileştirilmesidir.

Optimizasyon Süreci Sınır koşulları ve tasarım kriterleri belirlenir Güncellenen değerler ile CF hesaplanır Tasarım parametrelerini içeren CF oluşturulur. Güncel CF< Hedef Evet Tasarım parametrelerinin başlangıç değerleri atanır Hayır Optimum tasarım için gerekli tasarım parametreleri elde edilir CF değeri hesaplanır Optimizasyon metodunun güncelleme işlemleri yapılır SON Sınır değerler sağlanıyor mu? Evet Hayır

Optimizasyon ile Hedeflenenler • Daha yüksek güvenilirlik: Dış koşullardaki (sıcaklık, nem, vs) ani ve/veya şiddetli değişime rağmen devrenin yüksek doğrulukla çalışabilmesi. • Daha küçük toplam alan: Transistör boyutlarının azaltılması ve serimin daha az alan kaplaması • Daha düşük güç tüketimi: Daha uzun pil ömrü ve daha az ısınma problemi • Daha yüksek performans: Kazancın, band genişliğinin, giriş ve çıkış aralığının arttırılma, gürültü ve besleme gerilimi etkilerine daha az duyarlı olması. • Daha düşük maliyet: Devrenin tasarım aşamasından üretimine kadar olan süreçteki hem maliyet hem zaman gibi giderlerin düşürülmesi

Elektronik Devrelerde Optimizasyon • En uygun devre topolojisi seçimi • Optimum eleman boyutlandırma • Serim optimizasyonu

--Optimum Eleman Boyutlandırma Çalışmaları-- • Analog Devrelerde Optimizasyon • Analog Ayrık Devrelerde Optimizasyon “Filtre Devrelerinde Pasif Eleman Seçimi” • Analog Entegre Devrelerde Optimizasyon “CMOS İşlemsel Kuvvetlendirici Tasarımı” • Sayısal Devrelerde Optimizasyon • Sayısal Ayrık Devrelerde Optimizasyon “İşlevsel Lojik Devre Oluşturma” • Sayısal Tümleşik Devrelerde Optimizasyon “Lojik Kapıların Boyutlandırılması” “FPGA Optimizasyonu”

Analog Ayrık Devrelerde Optimizasyon Filtre Devrelerinde Pasif Eleman Seçimi Problem Tanımı:Hedef kriterleri (köşe frekans ve kalite faktörü değerlerini) minimum hata ile sağlayacak, endüstriyel üretim serileri ile uyumlu eleman değerlerine sahip filtre devresi tasarımı Eleman Değerleri: (Üretim Serileri:E12, E24, E48, E96, E192) + (Dekat Aralığı : 1kΩ-1MΩ, 1nF-1µF) Geleneksel Yöntem:Eleman değerlerinin hesabı tasarım kriter formüllerine göre hesaplanır. Birbirine eşit seçilen bazı ayrık eleman değerlerine bağlı olarak elde edilen diğer değerler, üretim serisi değerleri ile örtüşmeyebilir. Devrenin performansı, seçilen en yakın tercih edilen değerlere bağlı olarak düşebilir ve hata değerinin artmasına sebep olur

Filtre Devrelerinde Pasif Eleman SeçimiVCVS Butterworth Aktif Filtre Tasarım Denklemleri :

VCVS Butterworth Aktif Filtre Tasarım Kriterleri : E12 serisine uygun ayrık eleman değerleri : • ωc1, ωc2 = 10k rad/sn • Q1= 1/0.7654 • Q2 = 1/1.8478 Tasarım Denklemleri :

VCVS Butterworth Aktif Filtre Optimizasyonu** • Tasarım kriterleri ve denklemleri, tasarım parametrelerinin alabileceği değer aralığı ve varsa tasarımcı tarafından yapılan diğer tanımlamalar ve kısıtlar optimizasyon programına tanıtılır. • Optimizasyon algoritması toplam hata değerini minimize edecek ayrık eleman değerlerini bulur. ** Vural R.A. et al. (2012), “Performance Evaluation of Evolutionary Algorithms for Optimal Filter Design” IEEE Transactions on Evolutionary Computation, vol:16, issue:1, pp:135-147.

--Optimum Eleman Boyutlandırma Çalışmaları-- • Analog Devrelerde Optimizasyon • Analog Ayrık Devrelerde Optimizasyon “Filtre Devrelerinde Pasif Eleman Seçimi” • Analog Entegre Devrelerde Optimizasyon “CMOS İşlemsel Kuvvetlendirici Tasarımı” • Sayısal Devrelerde Optimizasyon • Sayısal Ayrık Devrelerde Optimizasyon “İşlevsel Lojik Devre Oluşturma” • Sayısal Tümleşik Devrelerde Optimizasyon “Lojik Kapıların Boyutlandırılması” “FPGA Optimizasyonu”

Analog Entegre Devrelerde Optimizasyon CMOS İşlemsel Kuvvetlendirici Tasarımı Problem Tanımı:Hedef kriterleri (güç tüketimi, kazanç, CMRR, PSRR, Faz marjini, vs…) ve tasarım parametre kısıtlarını sağlayacak, minimum MOS alanı kaplayacak işlemsel yükselteç tasarımı MOSFET W,L Değerleri: 100≥(W/L)1..8≥2 , (L1..8=2 µm) , W>=2*L Spesifikasyonlar • Ortak Mod Bastırma Oranı (CMRR) • Giriş Ofset Gerilimi (Vos) • Yükselme eğimi (SR) • Güç Tüketimi (Pdiss) • AC Karakteristikler (Av , ω-3dB , ft , f-3dB ) • Faz Marjini (o) • Giriş Ortak Mod Aralığı (ICMR) • Güç Kaynağı Bastırma Oranı (PSRR)

İki katlı işlemsel kuvvetlendirici Cc > (2.2/10)CL Id5=Cc*SR

Tasarım Denklemleri Cc’nin minimum değerini belirle. Cc > (2.2/10)CL SR’i sağlayacak Id5(Iss) değerini belirle. Id5=Cc*SR Farksal katın geçiş iletkenliği değerini kullanarak W1/L1(W2/L2)değerini bul ICMR üst sınır değerini sağlayan minimum W3/L3 (W4/L4) değerini bul. ICMR alt sınır değerini sağlayan minimum W5/L5 (W8/L8) değerini bul. Denge koşullarına göre W6/L6 değerini bul. İstenen akım oranlarına göre (W7/L7) değerini bul. Hedef kazanç ve güç tüketimi değerlerinin sağlandığını kontrol et. Tasarım parametrelerinin tam değerlerinin kullanıldığı CF<Hedef Hata olana kadar iterasyonlara devam et.

2 Katlı İşlemsel Yükselteç Algoritma Giriş Çıkış Bilgileri Tasarım Kriterleri : • SR≥10V/µs (CL=10pF) • ft ≥ 3MHz (CL=10pF) • Av> 1000 V/V • -1.5V≤ ICMR≤2V • Pdiss≤2.5mW • Area ≤ 300µm2 Toplam MOS Transistör Alanı :

Vektörel Bilgi: x = [SR, CL, Av,ft ,Vicmin, Vicmax, Pdiss] Toplam Alan

İşlemsel Kuvvetlendirici Optimizasyonu ** ** Vural R.A., Yildirim T., (2012), “Analog Circuit Sizing via Swarm Intelligence”, (Article In Press) , AEU - International Journal of Electronics and Communications, Elsevier.

--Optimum Eleman Boyutlandırma Çalışmaları-- • Analog Devrelerde Optimizasyon • Analog Ayrık Devrelerde Optimizasyon “Filtre Devrelerinde Pasif Eleman Seçimi” • Analog Entegre Devrelerde Optimizasyon “CMOS İşlemsel Kuvvetlendirici Tasarımı” • Sayısal Devrelerde Optimizasyon • Sayısal Ayrık Devrelerde Optimizasyon “İşlevsel Lojik Devre Oluşturma” • Sayısal Tümleşik Devrelerde Optimizasyon “Lojik Kapıların Boyutlandırılması” “FPGA Optimizasyonu”

Sayısal Ayrık Devrelerde Optimizasyon İşlevsel Lojik Devre Oluşturma • Lojik fonksiyonu karmaşık, giriş ve çıkış sayısı büyük tasarımlarda, Karnaugh haritası gibi yöntemler kullanılmaz. • Basit donanımsal gerçeklemeler için fonksiyonu yerine getirecek minimum sayıda lojik kapı içeren kombinezonsal devreler tercih edilir.

İşlevsel Lojik Devre Oluşturma (2) GA PSO DEPSO ** P. Moore and G. K. Venayagamoorthy, (2006)"Evolving digital circuits using hybrid particle swarm optimization and differential evolution ," Int. Journal of Neural Syst., vol. 16, no. 3, pp. 163-177.

İşlevsel Lojik Devre Oluşturma(3)** ** P. Moore and G. K. Venayagamoorthy, (2006)"Evolving digital circuits using hybrid particle swarm optimization and differential evolution ," Int. Journal of Neural Syst., vol. 16, no. 3, pp. 163-177.

--Optimum Eleman Boyutlandırma Çalışmaları-- • Analog Devrelerde Optimizasyon • Analog Ayrık Devrelerde Optimizasyon “Filtre Devrelerinde Pasif Eleman Seçimi” • Analog Entegre Devrelerde Optimizasyon “CMOS İşlemsel Kuvvetlendirici Tasarımı” • Sayısal Devrelerde Optimizasyon • Sayısal Ayrık Devrelerde Optimizasyon “İşlevsel Lojik Devre Oluşturma” • Sayısal Tümleşik Devrelerde Optimizasyon “Lojik Kapıların Boyutlandırılması” “FPGA Optimizasyonu”

Sayısal Entegre Devrelerde Optimizasyon Lojik Kapıların Boyutlandırılması-1 ** Optimizasyon Problemi • ** S. P. Boyd, S.J. Kim, D. D. Patil, and M. A. Horowitz, (2005) “Digital circuit optimization via geometric programming,” Operations Reserach., vol. 53, no. 6, pp. 899–932.

Lojik Kapıların Boyutlandırılması-2** • Klasik çok girişli lojik kapılar, çıkışta değişime sebep olan girişe bağlı olmaksızın aynı giriş çıkış gecikmesine sahip olacak şekilde tasarlanır. • Aktif güç tüketimini minimize etmek için Değişken Giriş Gecikmesine (VID) sahip lojik kapılar tercih edilir. • Bu kapılar farklı giriş-çıkış yolları için farklı gecikmeler sağlar. • Kapı içindeki herhangi iki yol arasındaki en yüksek gecikme farkı : “ub” ** T. Raja, V. D. Agrawal, and M. L. Bushnell, (2006), "Transistor sizing of logic gates to maximize input delay variability," Journal of Low Power Electronics, vol. 2, no. 1, pp. 121-128

--Optimum Eleman Boyutlandırma Çalışmaları-- • Analog Devrelerde Optimizasyon • Analog Ayrık Devrelerde Optimizasyon “Filtre Devrelerinde Pasif Eleman Seçimi” • Analog Entegre Devrelerde Optimizasyon “CMOS İşlemsel Kuvvetlendirici Tasarımı” • Sayısal Devrelerde Optimizasyon • Sayısal Ayrık Devrelerde Optimizasyon “İşlevsel Lojik Devre Oluşturma” • Sayısal Tümleşik Devrelerde Optimizasyon “Lojik Kapıların Boyutlandırılması” “FPGA Optimizasyonu”

FPGA Mimarisi • Programlanabilir mantık blokları (CLB), ara bağlantılar içerisine gömülü şekilde bulunur. • Programlanabilir mantık bloklarının yapılandırılması ve bu bloklar arasındaki iletişim ara bağlantılar sayesinde gerçekleşir. • Giriş çıkış blokları, ara bağlantılar ile bütünleşmiş devrenin paket bacakları arasındaki ilişkiyi sağlar.

FPGA Optimizasyonu • Yerleşim Problemi: • Lojik blokların fiziksel düzenlenmesidir. • FPGA performansını belirler. • Yönlendirme Problemi: • CLB I/O Bloklar ile metal hatların arabağlantı işlemidir. • Gecikmelerin minimize edilmesi gerekir.

PSO Tabanlı FPGA Yerleşimi ve Yönlendirmesi** • Xilinx FPGA üzerindeki 4 bit ALU uygulaması • 196 CLB: 14x14matris / ALU uygulaması için 13 CLB kullanılıyor. • PSO, CLBler arasındaki bağlantı uzunlarını minimize etmiştir. Son Durum İlk Durum ** Venu G. Gudise, Ganesh K. Venayagamoorthy. (2004) “FPGA Placement and Routing Using Particle Swarm Optimization”, Proc. of IEEE Computer Soc. Ann. Symp. on VLSI, pp.307-308.

Sorularınız …. Yrd. Doç. Dr. Revna ACAR VURAL Elektronik ve Haberleşme Müh. Böl. Elektronik A. B. D racar@yildiz.edu.tr