Chip Level Multithreading (CMT)

120 likes | 276 Vues

Chip Level Multithreading (CMT). By:- Tanveer Ahmed. Agenda . Introduction to CMT Programming Model. Background Terminology. General CMT behavior. Classes of CMT registers. CMT Registers. Parking Virtual registers. Performance Issues for CMT Processors. Introduction.

Chip Level Multithreading (CMT)

E N D

Presentation Transcript

Chip Level Multithreading(CMT) By:- Tanveer Ahmed

Agenda • Introduction to CMT Programming Model. • Background Terminology. • General CMT behavior. • Classes of CMT registers. • CMT Registers. • Parking Virtual registers. • Performance Issues for CMT Processors.

Introduction • All UltraSPARC IV+ processors use CMT Programming Model. • Specifies the basic functionality for controlling multi-core processor. • Defines how logical processors are identified.

Background Terminology • Thread. • Strand. • Pipeline • Physical Core. • Processor. • Virtual Processor.

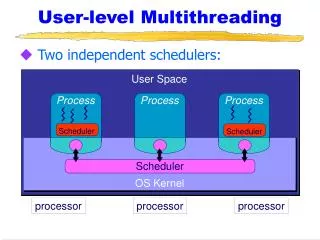

General CMT behavior • Virtual Processors are Independent in functionality. • OS treats a virtual processor as independent processor

Classes of CMT registers. • Two main classes: • Private Registers: A Private copy of the register is associated with each logical processor. • Shared Registers: A single copy of the register is shared by all the logical processors. • Both can be accessed by privileged software's. • One processor cannot access others private registers.

CMT Registers • Two Main Registers: • Strand ID Register (STRAND_ID): • Strand Interrupt ID Register (STRAND_INTR_ID)

Disabling and Parking Virtual Registers. • CMT provides the ability to disable virtual processors and park them. • Key Register used:- • Strand Available Register:- • Strand Enable Status Register:-

Disabling and Parking Virtual Registers Cont… • Strand Enable Register:- • Strand Running Register:-

Addition Info • Boot Sequence. • Resets and Trap Handling.

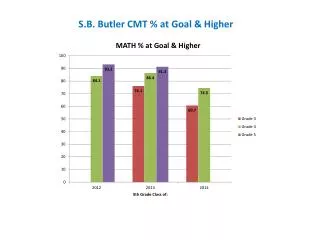

Performance Issues. • Shared Resources. • Needs complicated algorithms to make use of functionality. • Need knowledge of underlying architecture for programming.