8086 Hardware Specifications

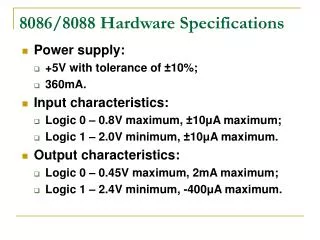

8086 Hardware Specifications. Agenda. Minimum & Maximum Mode Operations 8086 Pinout & Pin Functions Clock Generator (8284A) Bus Buffering & Latching System Bus Timing Read & Write Bus Cycles Ready & Wait States. Minimum & Maximum Mode Operations.

8086 Hardware Specifications

E N D

Presentation Transcript

Agenda • Minimum & Maximum Mode Operations • 8086 Pinout & Pin Functions • Clock Generator (8284A) • Bus Buffering & Latching • System Bus Timing • Read & Write Bus Cycles • Ready & Wait States

Minimum & Maximum Mode Operations • The 8086 can operate in either one of two modes of operation: • (1) Minimum Mode • (2) Maximum Mode • Minimum Mode: • The simplest and least expensive mode. • All the control signals for memory & I/O operations are generated by the processor. • Maximum Mode: • Allows the system to use an external coprocessor such as 8087 (floating-point coprocessor) . • Some of the control signals must be externally generated (requires an external bus controller 8288)

8086 Pinout & Pin Functions • AD15-AD0: • These lines represent time multiplexedaddress and data bus lines. • During T1, they represent address lines A15-A0. • During T2, T3, Tw, T4, they represent data lines D15-D0.

8086 Pinout & Pin Functions • A19/S6-A16/S3: • These lines represent time multiplexedaddress and status lines. • During T1, they represent address lines A19-A16. • During T2, T3, Tw, T4, they represent status signals S6-S3.

8086 Pinout & Pin Functions • ALE (Address Latch Enable ): • This signal is a HIGH pulse active during T1 of any bus cycle. • It is provided by the processor to latch the address lines during T2, T3, Tw, T4 cycles.

8086 Pinout & Pin Functions • Ready: • Active HIGH signal. • This is the acknowledgement from the addressed memory or I/O device that it will complete the data transfer. • If it is set LOW, the processor enters into wait states and remains idle. • If it is set HIGH, it has no effect on the operation of the processor.

8086 Pinout & Pin Functions • INTR (Interrupt Request): • It is used to request a hardware interrupt. • If it is held HIGH when IF (intr. flag)= 1, the processor enters an interrupt acknowledge cycle after the current instruction complete execution. • INTA (Interrupt Acknowledge): • This signal is a response to the INTR input pin. • NMI (non-Maskable Interrupt): • Similar to INTR except that NMI does not check if the IF=1.

8086 Pinout & Pin Functions • TEST: • Active LOW signal. • This input is examined by the WAIT instruction. • If the TEST input is LOW execution continues, • Otherwise the processor waits in an IDLE state. • Usually this pin is connected to the 8087 FP (floating point) coprocessor.

8086 Pinout & Pin Functions • RESET: • RESET causes the processor to immediately terminate its present activity. • The signal must be active HIGH for at least four clock cycles. • The processor restarts execution, when RESET returns LOW.

8086 Pinout & Pin Functions • CLK (Clock): • CLOCK provides the basic timing for the processor and bus controller. • It is asymmetric with a 33% duty cycle (HIGH for 1/3 of the clocking period and LOW for 2/3 of the clocking period) to provide proper internal timing.

8086 Pinout & Pin Functions • Vcc (+5v Power Supply) • GND (Ground) • MN/MX (Minimum/Maximum): • indicates what mode the processor is to operate in. • HIGH minimum mode. • LOW maximum mode.

8086 Pinout & Pin Functions • BHE/S7 (Bus High Enable): • Active low signal. • It is used together with A0 during T1 to select whole word, odd byte, even byte or none.

8086 Pinout & Pin Functions • M/IO (Memory/IO): • This pin is used to distinguish a memory access from an I/O access. • HIGH Memory access • LOW I/O access • It indicates that the processor address bus contains either a memory address or an I/O port address.

8086 Pinout & Pin Functions • RD (READ): • Active LOW signal • Read strobe indicates that the processor is performing a memory or I/O read cycle, depending on the state of the M/IO signal. • WR (WRITE): • Active LOW signal • Write strobe indicates that the processor is performing a memory write or I/O write cycle, depending on the state of the M/IO signal.

8086 Pinout & Pin Functions • DT/R (Data Transmit/Receive): • Needed in minimum system that desires to use a data bus transceiver. • It is used to control the direction of data flow through the transceiver. • HIGH Transmit • LOW Receive

8086 Pinout & Pin Functions • DEN(Data Enable): • Active LOW signal • Needed in minimum system that desires to use a data bus transceiver. • It is used as an output enable for the transceiver. • HIGH Enable • LOW Disable

8086 Pinout & Pin Functions • HOLD: • This input requests a direct memory access (DMA) • If this input is HIGH, the processor stops executing & places its address, data, and control bust at high-impedance state. • If this input is LOW, the processor executes software normally. • HLDA (Hold Acknowledge): • This signal indicates that the processor has entered the hold state

Clock Generator (8284A) • The 8086 CPU has 16 data lines and 20 address lines. • The CPU uses time multiplexing for the Address, data, and some status lines. • The Clock Generator and Driver 8284 is a device capable of providing the CPU with • Clock, • Reset Logic, and • Ready Logic.

Microcomputer System Design • A very simple microcomputer system consists of the following part: • (1) 8284A Clock Generator (15 MHz Crystal) • (2) 8086Microprocessor(Minimum Mode) • (3) Bus System (Demultiplexed and Buffered) • (4) Memory System (ROM & RAM Modules) • (5) I/O System (Switches and LEDs)

8086 Microprocessor (Minimum Mode) • Basic Connections: • GND: connect to 0V. • VCC: connect to 5V. • MN/MX’: connect to 5V (minimum mode). • NMI & INTR: connect to 0V (no support for interrupts). • CLK: connect to the CLK output of the clock generator. • HOLD: connect to 0V (no direct memory access). • TEST’: connect to 0V (no wait for co-processor). • READY: connect to 5V (no wait cycles for slow devices). • RESET: connect to RESET output of the clock generator.

5V 0V 5V 0V 0V 0V 0V 5V (8284A) CLK RESET (8084A) 0V

8086 Bus SystemThree Buses • The 8086 has three buses • (1) Address Bus: provides memory and I/O with the memory address or the I/O port number • (2) Data Bus: transfers data between the microprocessor and the memory and I/O • (3) Control Bus: provides control signals to the memory

Bus System DesignRequirements • Requirements: bus design must satisfy two main requirements • (1) Bus Buffering:the system must be buffered if the number of devices interfaced to it is more than its fan-out • (2) Bus Demultiplexing (Latching):All time multiplexed lines of the processor must be first demultiplexed (latched) to split address, data, status and control lines before interfacing them to memory and I/O devices.

Bus System DesignProcedure • Designing a bus system involves the following steps: • (1) Identify input, output and input/output pins of the processor. Note that only output and input/output pins are considered for designing the bus system (i.e. input pins are not part of the bus system). • (2) Identify time multiplexed pins of the processor. These pins need to be demultiplexed. • (3) Use latches to demultiplex time multiplexed pins. • (4) Use buffers to buffer all data, address and control lines to be connected to memory and I/O devices. • Latched lines are already buffered. • Input/output lines require bidirectional buffers • Output lines require unidirectional buffers

Bus Design Example (8086)(1) Identify Inputs, Inputs/Outputs & Outputs • Inputs: these are not part of bus system design • VCC • GND • NMI • INTR • CLK • RESET • READY • TEST’ • HOLD • MN/MX’

Bus Design Example (8086)(1) Identify Inputs, Inputs/Outputs & Outputs • Outputs: • A16/S3 • A17/S4 • A18/S5 • A19/S6 • RD’ • HOLDA (not required, why?) • WR’ • M/IO’ • DT/R’ • DEN’ • ALE • INTA’ (not required, why?)

Bus Design Example (8086)(1) Identify Inputs, Inputs/Outputs & Outputs • Inputs/Output: • AD0-AD15

Bus Design Example (8086)(2) Identify Time Multiplexed Pins • Time Multiplexed Pins: • AD0-AD15 • A16/S3-A19/S6 • BHE’/S7

Bus Design Example (8086)(3) Latching (Demultiplexing) Multiplexed Lines • As shown in Step(2), the 8086 has 21 multiplexed lines: • AD0-AD15 • A16/S3-A19/S6 • BHE’/S7 • To latch (demultiplex) these lines using 74LS373 octal latches, we need 21/8 = 3 chips. • The input controls of the 74LS373 octal latches should be connected as follows : • Output Control (OE’) connected to GND • Latch Enable (G’) connected to ALE

Bus Design Example (8086)(4) Buffering Address, Data & Control Lines • The data lines D15-D0 should buffered using bidirectional buffers (74LS245). • We have 16 data lines. So, we need 16/8 = 2 chips. • The Buffer Enable (G’) should be connected to DEN’ The Direction Control (DIR) should be connected to DT/R • The Control Lines M/IO’, RD’ and WR’ should be buffered using unidirectional buffers (74LS244). • The Buffer Enable (G’) should be connected to GND

Bus Design Example (8086)(4) Buffering Address, Data & Control Lines • Since address lines A19-A0 & BHE’ are latched using 74LS373 octal latches, they are already buffered. • The following control lines are will not be buffered: • DT/R’ & DEN’ because they are will not be connected to memory or I/O devices. • HOLDA because the direct memory access is not supported by our system. • INTA’ because interrupts are not supported by our system.

8086 Bus SystemBus Timing • 8086 access memory and I/O devices in periods called bus cycles. • Each cycle equals 4 system-clocking periods (T states). • If the clock is operated at 5 MHz, one 8086 bus cycle is complete in 800 ns.

8086 Bus SystemREADY and WAIT State • The READY input causes wait states for slower memory and I/O components. • A wait state (Tw) is an extra clocking period inserted between T2 and T3. • The READY input is sampled (checked) at the end of T2 and in the middle of Tw. • If READY is a logic 0 at the end of T2, then T3 is delayed and Tw is inserted between T2 and T3 • READY is next sampled at the middle of Tw to determine if the next state is Tw or T3. • The READY signal is synchronized with clock using the 8284A clock generator.

![8086 [2]](https://cdn1.slideserve.com/2457127/8086-2-dt.jpg)