Floating-point броеви

Floating-point броеви. За разлика од реалните броеви броевите со подвижна запирка не формираат континуум. Ако бројот не може да се изрази точно се користи најблискиот број, т.е. се изведува заокружување. n=f*10 e f - мантиса, е - експонент. Floating-point броеви.

Floating-point броеви

E N D

Presentation Transcript

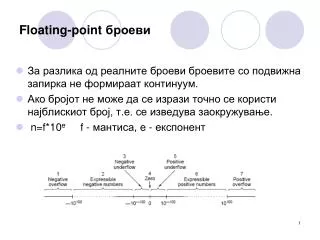

Floating-point броеви • За разлика од реалните броеви броевите со подвижна запирка не формираат континуум. • Ако бројот не може да се изрази точно се користи најблискиот број, т.е. се изведува заокружување. • n=f*10ef - мантиса, е - експонент

Floating-point броеви • Менување на број на цифри во мантиса или експонент дава подобра апроксимација или ги менува границите на регионите 2 и 6.

Floating-point броеви • Мантиса чија најлева цифра е 1 се нарекува нормализирана. • На следната слика е претставен процесот на нормализација на броеви со 16 битна матиса, 7 битен експонент и основа на експонентот 2 или 16. • За претставување на експонентот се користи вишок 64 нотација.

IEEE Floating-point Standard 754 (1985) • Стандардот е дело на William Kahan и дефинира 3 формати: • единечна прецизност (32 бита) • двојна прецизност (64 бита) • проширена прецизност (80 бита).

IEEE Floating-point Standard 754 (1985) • Двата формати почнуваат со бит за знак: 0-позитивен 1-негативен број. • Експонентот користи вишок вишок 127 нотација за експонентот во единечна прецизност. • Експонентот користи вишок вишок 1023 нотација за експонентот во двојна прецизност.

Примери - IEEE Floating-point стандард 754 со единечна прецизност • Бројот 0.5 во IEEE Floating-point стандард 754 со единечна прецизност хексадецимално се претставува 3F000000 • exp-127=126-127=-1 26+25+24+23+22+21=126 • 1.0*2-1 • Бројот 1во IEEE Floating-point стандард 754 со единечна прецизност хексадецимално се претставува 3F800000 • exp-127=127-127=0 26+25+24+23+22+21+20=127 • 1.0*20

Процесор – Организација и обработка на податоци Предавач: д-р Цвета Мартиновска Фонд на часови: 2+2

Data path – се состои од регистри (1-32), ALU и магистрали

ОБРАБОТКА НА ИНСТРУКЦИИ • КС ја изведува инструкцијата преку fetch-decode-execute циклусот: • CPU ја зема инструкцијата (ја пренесува од главна меморија во инструкциски регистер), • ја декодира (го определува кодот на операција и зема податоци потребни за да се изврши инструкцијата) и • ја извршува (ги изведува операциите дадени со инструкцијата). • Голем дел од fetch-decode-execute циклусот се троши на копирање податоци од една локација на друга.

ОБРАБОТКА НА ИНСТРУКЦИИ • Кога програмата се вчитува адресата на првата инструкција се става во PC. • Овој циклус се одвива во повеќе тактови на системскиот часовник. • Чекори на fetch фаза: • се копира содржината на PC во MAR: MAR<-PC • од главната меморија се зема инструкцијата која се наоѓа на адресата во MAR, се става оваа инструкција во IR, IR<-M[MAR], се зголемува PC за 1 (покажува на следна инструкција во програмата) PC<-PC+1

ОБРАБОТКА НА ИНСТРУКЦИИ • Бидејќи машината која ја разгледуваме е збор-адресибилна, инкрементирањето на PC за 1 доведува до тоа да адресата на следниот збор се најде во PC. • Ако машината е byte-адресибилна PC треба да се инкрементира за 2 за да покажува на адресата на следната инструкција бидејќи секоја инструкција се состои од 2 bytes. • Kaj byte-адресибилна машина со зборови од 32 бита PC треба да се инкрементира за 4.

ОБРАБОТКА НА ИНСТРУКЦИИ • Чекори на decode фаза: • се копираат најдесните 12 бита од IR во MAR, MAR<-IR[11-0] се декодираат најлевите 4 бита IR[15-12]. • Чекори на execute фаза: • ако е потребно се користи адресата од MAR за да се земат податоци од меморијаподатоците се ставаат во MBR (или AC), MBR<-M[MAR] и се извршува инструкцијата.

ИНТЕРАПТИ И В/И • Машината која ја разгледуваме има 2 регистри за работа со влезни и излезни уреди. Во влезниот регистер се сместени податоци префрлени од влезниот уред а во излезниот регистер информации кои треба да се испратат на излезен уред. • Потребно е процесорот и В/И да се временски усогласени. • (Пример: Ако процесорот е побрз од тастатурата ќе го прочита истиот податок повеќе пати, или • ако внесувањето е побрзо од читањето податок од влезниот регистер може да се изгуби внесен податок) • Проблемот се решава со В/И управувани со интерапти.

ИНТЕРАПТИ И В/И • Кога влезот/излезот се завршени В/И уредот испраќа интерапт сигнал до CPU • CPU го обработува интераптот и потоа продолжува со прекинатиот fetch-decode-execute циклус. • Најголем број КС проверуваат дали е генериран интерапт на почеток на секој fetch-decode-execute циклус. • В/И уредите испраќаат интерапти со користење на status (flag) регистерот. Кога настанува интерапт се сетира бит од овој регистер, а CPU го проверува битот пред почеток на секој машински циклус.

ИНТЕРАПТИ И В/И Проверка дали треба да се обработи интерапт се извршува пред секој инструкциски циклус.

ИНТЕРАПТИ И В/И • Обработување на интерапт е извршување на интерапт рутина. • Пред да се изврши рутината содржината на сите регистри на CPU треба да се зачува, а по завршување на рутината да се врати во регистрите. • Други интерапти • надворешни (прекин на напојување) • внатрешни (делење со нула, stack overflow, protection violations) • софтверски (програмски премин од извршување програма на наредба од оперативен систем)

АСЕМБЛЕРСКА ПРОГРАМА ЗА СОБИРАЊЕ 2 БРОЈА Програмата собира два броја и резултатот го сместува во меморија. Во втората колона е асемблерската програма а во третата истата програма во машински јазик.Третата колона е содржината на меморијата претставена во хексадецимален код.

СОБИРАЊЕ 2 БРОЈА • Fetch-decode-execute циклусот почнува со полнење на првата инструкција на програмата, која се наоѓа со полнење на PC со адресата на првата инструкција. Програмата почнува од адреса 100H. • Се извршува Load на 002316 (3510) во AC. • Потоа се собира со FFE916 (-2310) кое се наоѓа на адреса 105, при што се добива резултат 12 во AC. • Инструкцијата Store ја сместува вредноста на мемориска локација 106.

СОДРЖИНА НА РЕГИСТРИ ЗА ПРОГРАМАТА ЗА СОБИРАЊЕ 2 БРОЈА

СОДРЖИНА НА РЕГИСТРИ ЗА ПРОГРАМАТА ЗА СОБИРАЊЕ 2 БРОЈА

СОДРЖИНА НА РЕГИСТРИ ЗА ПРОГРАМАТА ЗА СОБИРАЊЕ 2 БРОЈА

Асемблерски јазик, асемблирање • Асемлерот source file (асемблерска програма) го претвара во object file (машински код). • Поедноставно е пишување код со мнемоници (асемлерски јазик) отколку со машински код. • Поедноставно е мемориската адреса да се замени со лабела. • При асемблирање на програма која користи лабели мора да се направат 2 поминувања низ програмата за да се преведе во машински код. • При првото поминување низ кодот асемблерот гради табела на симболи (не може веднаш да се генерира машински код бидејќи не знае каде се сместени податоците на инструкцијата ако е дадена само лабела.)

Пример: програма која користи лабели • Табела на симболи креирана при првото поминување на асемблерот низ програмата:

Пример: програма која користи лабели • Асемблерот исто така започнува да ги преведува инструкциите. При првото поминување преведените инструкции ќе бидат некомплетни: • При второто минување асемблерот ја користи табелата на симболи за да ги пополни адресите и да креира соодветни инструкции во машински јазик.

Асемблерски директиви • Асемблерска директива е инструкција која не се преведува во машински код. • DEC -асемблерска директива која овозможува податоците да се внесат како декадни броеви. • HEX-асемблерска директива која овозможува податоците да се внесат како хексадекадни броеви. • / - асемблерска директива која означува дека текстот кој следи по неа е коментар Пример: користење директиви за константи

ПРОШИРУВАЊЕ НА ИНСТРУКЦИСКОТО МНОЖЕСТВО • Во машината која ја разгледуваме предвидени се 4 бита за код на операција. Досега разледавме 9 операции. Множеството на инструкции се проширува со следните 4 инструкции:

ПРОШИРУВАЊЕ НА ИНСТРУКЦИСКОТО МНОЖЕСТВО • JnS (jump-and-store) - се чува покажувач за враќање на местото од кое е повикана друга процедура. • Clear - сместува 0 во AC. • AddI како и JumpI - користи индиректен начин на адресирање. Наместо вредноста на локација X да се смета за адреса, се користи вредноста најдена на локација X како покажувач до нова мемориска локација која содржи податок кој се користи во инструкцијата.

РЕГИСТАРСКИ ПРЕНОС КАЈ ИНСТРУКЦИИТЕ

КОМПЛЕТНО ИНСТРУКЦИСКО МНОЖЕСТВО НА МАШИНАТА

ПРИМЕР:ПОВИКУВАЊЕ ПОТПРОГРАМА ЗА ДУПЛИРАЊЕ НА БРОЈ

ДЕКОДИРАЊЕ: HARDWIRED ИЛИ МИКРОПРОГРАМИРАЊЕ • Како функционира контролната единица? • Hardwired - директна секвенцијална логика, физичко поврзување на контролни линии и машински инструкции. • Се користи дигитално коло во кое влезови се битови на opcode од инструкциите, битови од status регистерот, сигнали од магистралата и од системскиот часовник. Излези се контролни сигнали кои управуваат со компонентите на КС. • Со користење на содржината на IR и статусот на ALU оваа единица ги контролира регистрите, ALU операциите, поместувачите и пристапот до магистралата.

ПРЕДНОСТИ И НЕДОСТАТОЦИ НА HARDWIRED КОНТРОЛА • Предност: операциите се одвиваат побрзо отколку кај микропрограмирање. • Недостаток: инструкциското множество и контролната логика се директно поврзани со специјални кола кои се комплексни и тешко се дизајнираат или менуваат.

МИКРОПРОГРАМИРАЊЕ • Сите машински инструкции се влез во специјална програма, микропрограма, која ги конвертира инструкциите во соодветни контролни сигнали. • Микропрограмата е интерпретер напишан во микрокод и сместен во firmware (ROM, PROM, EPROM). Таа ги конвертира машинските инструкции од нули и единици во контролни сигнали. За секоја машинска инструкција постои посебна потпрограма. • Предност: измената на инструкциското множество се остварува со update на микропрограмот. • Недостаток: Инструкциите поминуваат низ дополнително ниво на интерпретација што го забавува извршувањето на програмата.

CISC и RISC архитектури • CISC –имаат голем број инструкции со различна должина. Многу од овие инструкции изведуваат повеќе операции. • RISC – мало но комплетно множество инструкции, реализирано хардверски. Инструкциите се поедноставени за брзо извршување. Секоја инструкција изведува една операција. Инструкциите имаат иста големина и сите аритметички операции мора да се изведуваат меѓу операнди во регистри. • Инструкциските множества од 1982 година се RISC или комбинација на RISC и CISC.

CISC и RISC архитектури • RISC – Во 1980 група од Berkeley, предводена од David Patterson и Carlo Sequin почнала да дизајнира VLSI CPU чипови кои не користеле интерпретирање. • John Hennessy дизајнирал чип MIPS. • Овие чипови еволуирале во SPARC и MIPS.

Intel архитектури • Првиот популарен Intel чип 8086 епроизведен во 1979 и е употребен во IBM PC: • Користел 16 bits податоци, 20 bits адреси, па можел да адресира милион bytes меморија. • Близок до 8086 е 8088 (8 bit екстерен бас) користен во IBM PC имал помала цена. • Во 8086 CPU е поделен на 2 дела: • Извршна единица (execution unit)која ги содржи регистрите за општа намена и ALU • Единица за поврзување со магистралата (bus interface unit)која содржи инструкциски ред (instruction queue), сегментни регистри и IP (instruction pointer)

Intel архитектури • 8086има четири 16 битни регистри за општа намена: • AX – примарен акумулатор • BX – базен регистер кој се користи за проширено адресирање (base register) • CX – бројачки регистер (count register) • DX – податочен регистер (data register) • Секој од овие регистри има 2 дела: most significant (AH, BH, CH, DH)и least significant (AL, BL, CL, DL) дел. • 8086 има 3 покажувачки регистри • Stack pointer (SP) – се користи како offset за стекот • Base pointer (BP) – за покажување кон параметри кои се вметнуваат на стек • Instruction pointer (IP) – ја чува адресата на следната инструкција

Intel архитектури • 8086има 2 индексни регистри • SI (source index) - покажувач на почетен стринг кај стринг операции • DI (destination index) – покажувач на одредиште кај стринг операции • Има и status flags регистер чии битови укажуваат на overflow, carry • Асемблерската програма кај 8086 е поделена на 3 сегменти, специјални блокови кои чуваат специфична информација: • Code segment – ја чува програмата • Data segment – ги чува податоците • Stack segment – го чува програмскиот стек • За пристап до информација во некој од овие сегменти потребно е да се специфицира поместување (offset)од почетокот на соодветниот сегмент.

Intel архитектури • Затоа се потребни сегментни поинтери за сместување на адресите на сегментите. Се реализираат со следните регистри: • CS (code segment) • DS (data segment) • SS (stack segment) • ES (extra segment) – се користи од некои операции со стрингови за адресирање на меморија. • Адресите се специфицираат користејќи segment:offset адресирање во форма xxx:yyy, каде xxx е вредност во сегментниот регистер а yyy е offset.

Intel архитектури • Во 1980 Intel го воведува 8087 кој додава floating-point инструкции на 8086 машинското множество, како и 80-битен стек. • Во 1982 го произведува 80286 • може да адресира 16 милиони bytesмеморија • Во 1985 го произведува 80386 • 32 битен чип, може да адресира 4 билиони bytes меморија • Поддршка за мултитаскинг • Имињата кај 32 битните регистри на 80386 вклучуваат префикс Е (наместо AX, BX, CX, DX се користи EAX, EBX, ECX, EDX). • Програмерите сеуште може да пристапат до AX, AL, AH

Intel архитектури • 80386 и 80486 се 32 битни машини со 32 битна магистрала • 80486 има пософистициран кеш и инструкциски цевковод и вграден математички копроцесор • Pentium серијата почнува со процесор со 32 битни регистри и 64 битна податочна магистрала, како и суперскаларен дизајн ( CPU има повеќе ALU и може да извршува повеќе од една инструкција во еден такт на системскиот часовник, односно изведува повеќе инструкции паралелно). • Pentium Pro • Подобрена суперскаларна организација • Предвидување на разгранувања • Анализа на податочниот проток

Intel архитектури • Pentium II • MMX технологија • графичко, видео и аудио процесирање • Pentium III • Дополнителни инструкции со подвижна запирка за 3D графика • Pentium II и Pentium III користат комбиниран приод, CISC архитектура со RISC јадра кои може да преведуваат од CISC во RISC инструкции. • Pentium 4 • Има брзина на системски часовник од 1.4 GHz, 42 милиони транзистори за CPU, се користи hyper-pipeline, 400 MHz системска магистрала, дополнителни floating point и cache memory подобрувања.

Intel архитектури • Во 2001 се произведува Itanium, 64 битен чип, кој воведува регистерски базиран програмски јазик и многу богато инструкциско множество. • Има хардверски емулатор за компатибилност со 32 битните архитектури и x86 архитектурите. • 4 integer единици, 2 floating point единици, значајно количество на кеш меморија на 4 различни нивоа, 128 floating point регистри, 128 integer регистри и повеќе регистри за општа намена за ефикасно земање инструкции при разгранување. • Може да адресира до 16 GB меморија.