Xetal-Pro: Innovative SIMD Computer Architecture for Computation Efficiency

Explore the Xetal-Pro's groundbreaking SIMD design for efficient computation in embedded computer architecture. With 320 PEs and 80GOPS, it sets new standards in programmable silicon. Learn about its memory access and advanced features.

Xetal-Pro: Innovative SIMD Computer Architecture for Computation Efficiency

E N D

Presentation Transcript

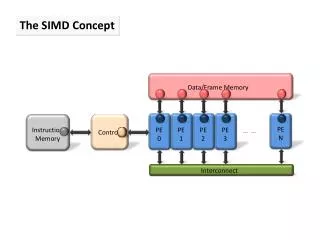

The SIMD Concept Data/Frame Memory PE N Instruction Memory PE 0 PE 1 PE 2 PE 3 … … Control Interconnect

Embedded Computer Architecture SIMD: XETAL and IMAP 5KK73 TU/e Henk Corporaal Bart Mesman

CPLD XETAL-II 8051 SRAM ZigBee Xetal-II

DOP DIP Frame Memory (2048 lines x 320 words) In Out Sequential I/O Memory (2 lines x 320 words) OMEM,LUT (240 kb) IMEM (240 kb) Linear Processor Array (320 PEs) GPI Data (2k x 16b) Program (16k x 56b) GPO I2C Xetal-II Processor • 600 mW • 90 nm CMOS • 53.5 GOPS (arithmetic only) @ 84MHz • Best computationalefficient programmable silicon in 2007 [Kleihorst, et al.2007]

Xetal-II Memory Access All PEs access the same line of the Frame Memory

IMAP Series Processors (NEC) Peak Performance(GOPS) ISSCC’03 1000 IMAP-CE 100MHz, 128PE/Chip 4-Way VLIW+MAC, 100GOPS (-40℃~85℃), 0.13 um, <2Watt 100MHz, 128PE/Chip 4-Way VLIW ,50GOPS 0.18um, 2~4Watt 100 IMAPCAR ISSCC’95 (PE8: eight PEs integration block) 10 11.0mm IMAP-2 CAMP’97 DPLL EXTIF 40MHz, 64PE/Chip IMAP-VISION PE8 PE8 PE8 40MHz, 32PE/Chip 1 PE8 PE8 PE8 CP 11.0mm IMAP-1 15MHz, 8PE /Chip PE8 PE8 PE8 PE8 PE8 0.1 PE8 PE8 PE8 PE8 PE8 1990 1995 2000 2005 2010 IMAP-CE(32.7M Tr, 0.18um) Year [Shorin Kyo, et al.2005]

IMAPCAR Block Diagram and Features 12.8 GByte/s ALUx1,MULx1,LOGx1,LSUx1 0.8 GByte/s To/Fr other PEs To/Fr CP To/Fr IMEM EMEM 0 IMEM 4 Way VLIW PE EMEM 1 IMEM 4 Way VLIW PE LOG MUL ADD RDU LSU COMM External Mem. I/F EMEM 24 x 8b General Purpose Registers 127 EMEM IMEM 4 Way VLIW PE 128 SR0 Control Processor (CP) SR1 Video OUT SR2 P$,D$,STK RAM SR3 Host Processor Video IN • 128 4-Way VLIW PEs • < 2W @ 100MHz • 130nm CMOS • 128 individual RAM blocks

IMAPCAR Memory Access: local addressing support Each PE could access different lines of the Memory Requires separate memory module per PE

XC Core: SIMD/MIMD 90nm CMOS, 108MHz [Shorin Kyo, et al.2009]

Xetal-Pro Memory Access • Characteristics: • 320 single-issue PEs • 80GOPS @ 125MHz • 65nm CMOS • 1pJ/op at sub-threshold All PEs access the same line of the Scratchpad Memory or Frame Memory