Abstract

Abstract. Semiconductor Industry Association. “ … a crisis is approaching”. • The challenges are the drastic increase of clock frequency and the exponential increase of circuit complexity. • The industry must move rapidly towards re-using more complex logic cells.

Abstract

E N D

Presentation Transcript

Semiconductor Industry Association “ … a crisis is approaching” • The challenges are the drastic increase of clock frequency and the exponential increase of circuit complexity. • The industry must move rapidly towards re-using more complex logic cells. • Standards for interfaces between blocks are essential. • The problem of simulating and verifying such chips has not yet been resolved. Taken from: The National Technology Road Map for Semiconductors Semiconductor Industry Association 1997 Edition

TRUEFALSE Wire encoded DATA data values TRUEFALSE TRUEFALSE INTERMEDIATENULL time encoded control hysteresisNULL hysteresisNULL The Choice The semiconductor industry is based on 2 Value Boolean logic. 2NCL 2NCL expresses the differentiation of DATA and control, but does not differentiate the expression of DATA values which: must be expressed extra-logically in terms of multi-rail data representation. 4NCL 3NCL Logically complete but impractical to implement. Still not quite practical to implement and less logically complete. compromise the expression of data 2NCL is the least compromise With only two logical values, one must chose which logical expressivity to compromise. compromise the expression of control Boolean logic expresses the differentiation of DATA values but, simply ignores the expression of control which: must be added extra-logically in terms of time (the clock). Boolean Logic

NCL Circuit Design • Circuits are designed using general M-of-N threshold gates with hysteresis. • The gate switches when M inputs are data, and when all N inputs are NULL. • Several static and dynamic design techniques are available, providing flexibility in speed/power tradeoffs. • Each gate is a synchronization node, there are no timing issues or race hazards. • Each circuit indicates its own completion resolution. (Indicates a Data or NULL state.) NCL Static 2-of-3 Threshold Gate

1 1 1 1 1 inverter equivalent OR gate equivalents 2 2 2 2 Minimal Subset Muller/DIMS equivalent 3 3 3 The occasional arbiter 4 4 A C element equivalents 5 The 2NCL Family of Logic Gates M of N threshold gates with hysteresis behavior A small cell family comprised of only Threshold Gates

Benefits of Self-Timed Logic • Lower power • No clock tree and long control lines to be driven • Gates which are not processing data are quiescent • Power supply can be reduced to match required data rate • Extremely low EMI and power/ground bus noise signatures • No clock to cause synchronized switching of large numbers of transistors. • More finely grained pipelining creating faster circuits • NCL homogeneous design style allows registration stages to be added at • low overhead NCL Improves System Performance

NCL Simplifies Chip Design Benefits of Self-Timed Logic-continued • Easy and reliable composability with simple integration of local circuits. • Clocks and attendant design complexities are eliminated. • Failures modes such as race hazards and clock skew are eliminated. • Collections of NCL chips and core self synchronize • Easy system portability among fabrication technologies. • NCL circuits are effectively delay insensitive, thus porting is a simple • design rule change. No detailed re-timing or new test vectors. • Improved system reliability in hostile and extremely varying environments. • Since NCL circuits are effectively delay insensitive they function • correctly over a wide range of power supply and temperature variations. • Improved system testability. • Only functional correctness and overall system throughput is required.

Robust/Reliable Operation Because NCL™ circuits are essentially delay insensitive they are also insensitive to power supply voltage. Correct circuit functionality is guaranteed while dynamically sweeping power supply voltage over a wide range, and with circuit speed and power dissipation varying over many orders of magnitude.

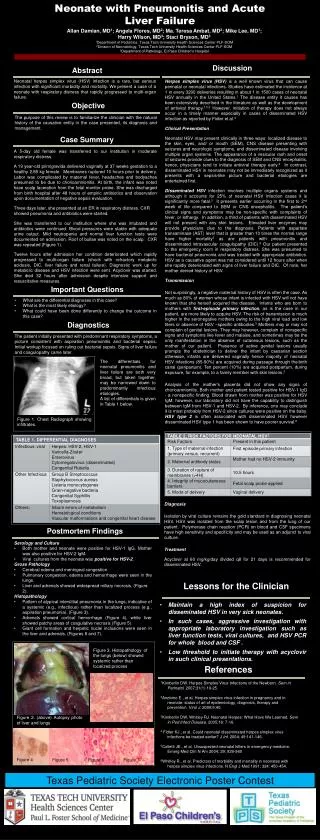

2 TAP NCL Finite Impulse Response Filter Demonstration • PCB with NCL Adder and Multiplier chips • Adder/Multiplier chips run at 50+ MHz • System automatically adjusts to slower speed because of board delays and runs at 30 MHz • System speed dynamically adjusts to changing power supply voltage and ambient temperature

NCL Digital Channelizer • 0.5 CMOS • 3 Level Metal • 420K Transistor • 200Mbs input CFB1 _ 5 CFB2 _ 6 IFFT _ BANK CFB3 _ 7 CFB4 _ 8

Cascade Processor • Performance increases are not limited by the ability to design and implement ever increasingly complex clock circuits • Capability to process heterogeneous instruction sets including legacy code such as Power PC or 1750A • Performance gains due to automatic processing of independent threads • Within a thread processor exploits concurrency by resolving dependencies • Concurrent processing of multiple instruction streams • Adaptive reconfiguration of processing resources Multiple reference streams Decoder library Function library Directive decoder ref Slot structure fFunction mapping environment next dir addr Function cache Memory Access Directive decoder ref I/O channels next dir addr directive decoder ref Results return next dir addr

SiO2 What is SOI? Items on this paper where collaborated on with G. Kirchner of Honeywell Solid State Electronics Center SOI CMOS Bulk CMOS Silicon Substrate Silicon Substrate TBOX = 300-375nm TSi = 200nm Region of high capacitance substantially reduced by buried oxide layer Buried oxide layer (BOX) formed by oxygen implantation (SIMOX) or wafer bonding and etchback (BESOI) • Unique Features of SOI CMOS • Junction capacitance reduced by over 3X • Transistors are completely isolated from each other • Reduced subthreshold source to drain leakage • Minimum transistor to transistor separation same as minimum lithography space • Device fabrication process approximately 10-15% less complex relative to bulk

Band Activity Detector (B.A.D.) Channel Activity Detector Wideband Detection Encoder (WDE) Det Data Thres Channel 1 Detection Qualifications from System ADC PolyPhase Channelizer 10 Det Data Thres CAD2 Channel 2 IF Input Det Data Thres CAD3 Channel 3 Existing Program SIG DET FREQ TO PW Complimentary IRAD Clockless Logic Program Activities (New) Data to Narrowband Receiver Subsystem Subband Activity Detector

Silicon On InsulatorTechnology at SSEC Items on this paper where collaborated on with G. Kirchner of Honeywell Solid State Electronics Center SiO2 insulating layer provides reduced capacitance and supports higher density • 40% to 100% faster circuits • 30% to 70% lower power • No latchup or soft errors • High temperature operation • Higher performance sensors Nonvolatile Memories System on a Chip Bulk CMOS Silicon Substrate Region of high capacitance substantially reduced by buried oxide layer Mixed Mode Digital Rad Hard SOI CMOS SiO2 SOI CMOS Silicon Substrate Sensors Integrated Hi Temp Sensor Systems • ASICs & memories • DoD & commercial space applications • 0.7 and 0.35 micron • In production since 1995 Hi Temp Electronics

Honeywell SOI CMOS Roadmap Items on this paper where collaborated on with G. Kirchner of Honeywell Solid State Electronics Center 95 96 97 98 99 00 01 02 03 04 400K Gate Array SRAM-Based FPGA 1M SRAM • SOI-IV 0.7µm • 5, 3.3, 2.5V • 3/4 level interconnect HX2000 300K Gate Array Family 5V Low Power Gate Arrays 3.3, 2.5V Mixed Mode ASICs Ultra Low Power Option 1.8V, 0.25µm 1.5M Gate Std Cell ASICs • SOI-V 0.35µm • 3.3, 2.5, 1.8V • 0.25µm gates for 1.8V • 4/5 level interconnect HX3000 1M Gate Array Family 3.3, 2.5V Mixed Mode ASICs Embedded Nonvolatile Memory Mixed Mode ASICs 4M SRAM 16M SRAM • SOI-VI 0.25µm • 2.5, 1.8, 0.9V • 4/5 level interconnect HX4000 4M Gate Std Cell ASICs 2.5, 1.8V Ultra Low Power Option 0.9V, DTC Mixed Mode ASICs • SOI-VII 0.15µm • 1.8, 0.9, 0.5V • 4/5 level interconnect HX5000 8M Gate Std Cell ASICs 64M SRAM

2 of 2 Threshold Gate • SOI5 (3.35µm) Silicon-on-Insulator Process • Semi-static Design Style (weak keepers) • Cell Height: 18 µm • Pin Pitch: 2 µm

Initial NCL SOI CMOS Cell Library Cell List The cells have been designed to enable 1:4 demultiplexer circuit to be fabricated on an initial test chip NC xor2 T22 T22b Th12 Th12b Th22 Th22s Th22n Th33 Th33d Th33n Th34i Buffer Inverter b - inverted output T = without hysteresis Th - Semistatic gate with weak feedback d - Set to Data n - Set to NULL

Unique Features of Honeywell’s SOI-BasedSystem-on-a-Chip Approach Items on this paper where collaborated on with G. Kirchner of Honeywell Solid State Electronics Center This combination of capabilities on one chip is unique in the IC industry Low Power Digital Logic - 30-50% higher performance and lower power than bulk silicon CMOS - Unique asynchronous standard cell library (Null Convention Logic) Analog/RF CMOS - SOI provides 10X noise reduction over existing technologies and much better isolation - Unique devices: MEMS inductors, T-gate MOSFETs, DMOS, CrSi resistors Nonvolatile GMR RAM - No one today offers fast embedded EEPROM with performance and density similar to SRAM and DRAM and no wearout SOI CMOS Core Technology Programmable Logic - Asynchronous version offers >40% better density and simplified programming over other solutions - GMR nonvolatile latches for configuration storage Sub 1V Operation - Only SOI supports active threshold control for high performance operation at 0.9V and below SiGe BICMOS - 1.5 to 2X higher performance devices when integrated with SOI - 150 to 300 GHz Ft Cold Sparing for zero power drain in off mode Usable Gates: 1.5M at 0.35m 4M at 0.25m

FIFO8 bits x 64 Words 16 16 8 8 BCLtoNCL NCLtoBCL NCL FIFO DATAOUT DATAIN BCL BCL ACKOUT ACKIN DEMUX MUX REQOUT DATA DATA DATA DATA REQIN BCLtoNCL NCL NCLtoBCL ACK ACK FIFO REQ REQ REQ REQ CLOCKIN2 CLOCKIN1 Clock Clock CLOCKOUT2 CLOCKOUT1 RESET NCL Universal Asynchronous Interface