Trade-offs in Performance, Power, and Area for Massively Parallel SuperCISC Architectures

This document explores the critical trade-offs between performance, power consumption, and area in the context of massively parallel SuperCISC hardware functions. Key insights include how reducing critical path lengths can significantly increase clock frequency and overall system performance, with replicated hardware leading to linear increases in power and area consumption. The impact of pipelining and hardware predication on improving throughput while managing energy costs is also discussed, highlighting a complex interplay between efficiency and resource allocation.

Trade-offs in Performance, Power, and Area for Massively Parallel SuperCISC Architectures

E N D

Presentation Transcript

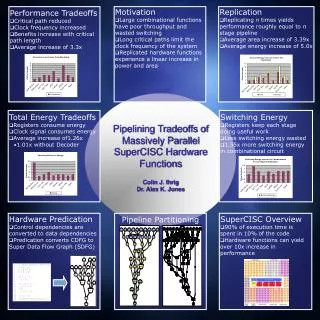

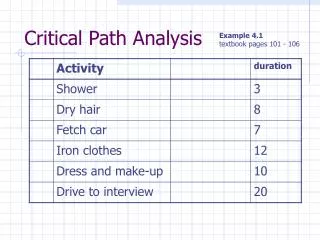

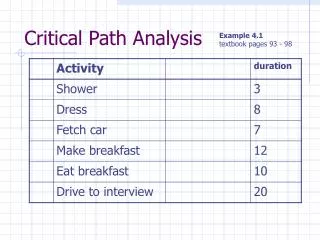

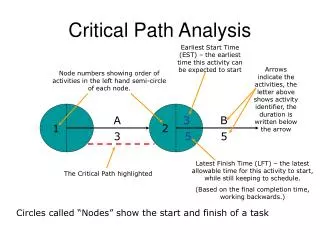

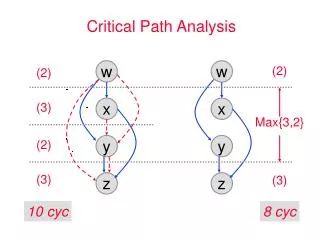

Performance Tradeoffs • Critical path reduced • Clock frequency increased • Benefits increase with critical path length • Average increase of 3.3x Motivation • Large combinational functions have poor throughput and wasted switching • Long critical paths limit the clock frequency of the system • Replicated hardware functions experience a linear increase in power and area Replication • Replicating n times yields performance roughly equal to n stage pipeline • Average area increase of 3.39x • Average energy increase of 5.0x • Total Energy Tradeoffs • Registers consume energy • Clock signal consumes energy • Average increase of1.26x • 1.01x without Decoder Switching Energy • Registers keep each stage doing useful work • Less switching energy wasted • 1.55x more switching energy in combinational circuit Pipelining Tradeoffs of Massively Parallel SuperCISC Hardware Functions Colin J. Ihrig Dr. Alex K. Jones Hardware Predication • Control dependencies are converted to data dependencies • Predication converts CDFG to Super Data Flow Graph (SDFG) • Pipeline Partitioning SuperCISC Overview • 90% of execution time is spent in 10% of the code • Hardware functions can yield over 10x increase in performance 1 // Begin HardwareFunction 2 z = x + y; 3 m = y << 3; 4 n = m – y; 5 6 if(n < 0) 7 n = 0; 8 9 if(q == 3) 10 i = z + 5; 11 else 12 i = z – 2; 13 14 j = n * i; 15 //End Hardware Function