WINLAB CR Platform

WINLAB CR Platform. Ivan Seskar Rutgers, The State University of New Jersey www.winlab.rutgers.edu Contact: Ivan Seskar, Associate Director s eskar (at) winlab (dot) rutgers (dot) edu. Cognitive Radio (CR) p latforms.

WINLAB CR Platform

E N D

Presentation Transcript

WINLAB CR Platform Ivan Seskar Rutgers, The State University of New Jersey www.winlab.rutgers.edu Contact: Ivan Seskar, Associate Director seskar (at) winlab (dot) rutgers (dot) edu

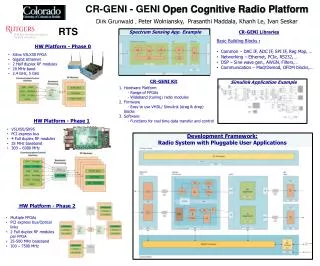

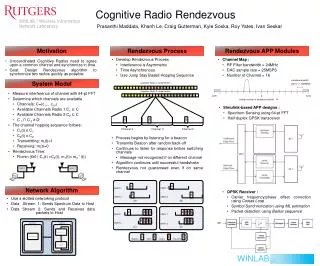

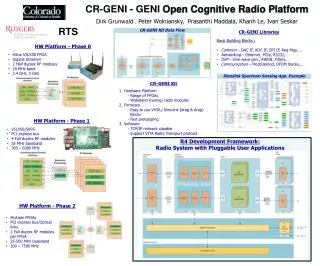

Cognitive Radio (CR) platforms • Research community already has a variety of platforms for CR research Microsoft Sora USRP2 USRP WINLAB WINC2R System U. Of Colorado RICE WARP Platform

Cognitive Radio platform issues • Problems with existing (experimental) platforms: do we wait for Moore’s law to catch up or we need new hardware architectures for CR? • “Analog” issues: range (frequency, power), agility, cost, scalability, future proofing • “Digital” issues: scalability, power consumption, performance vs. flexibility, cost, future proofing • Ease of “use” issues: how do we program/control these platforms? • Large scale experiments in realistic environments • Nation-wide (experimental) cognitive radio spectrum allocation • Multiple testbeds with different objectives • GENI advanced technology demonstrator of cognitive radio networks • Address New Application Needs • Spectrum sensing, vehicular networking

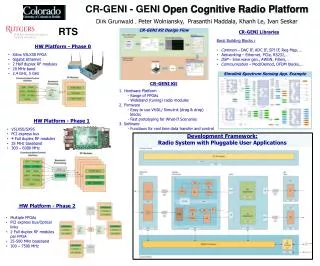

Spiral II GENI project: CR kit • Range of baseband FPGA platforms • 4 (2) configurable radio modules for phased or smart antenna applications with • Phase I: Each module allows two 25 MHz bands from 300 to 6000 MHz • Phase II: Each module allows two different 300 MHz bands from 100 to 7500 MHz • Each module supports independent full duplex operation. • 1 usec RF frequency switching time • Switched antenna diversity for both TX and RX channels.n Wideband Digital Radio (WDR) block diagram

CR Kit Timeline • 2/1/10 - Redesign, manufacturing, testing and integration of frequency-extended Phase I radio card for use in stand-alone cognitive radio system. • 3/16/10 - Integration of Phase I radio card with off-the-shelf components to develop a stand-alone cognitive radio platform; validation with basic tests; demonstration • 7/20/10 - Initial integration of stand-alone cognitive radio platform with v0.1 software, initial integration into ORBIT Management Framework, and demonstration. • 7/20/10 - Make stand-alone cognitive radio system available for use by selected (GENI) researchers. • 9/30/10 - Release a full set of design information for stand-alone cognitive radio system “kit”, including hardware and v0.1 software. • 12/1/10 - Design, manufacturing, testing and integration of infrastructure-class Phase II radio card featuring wideband operation, for use in stand-alone and infrastructure class cognitive radio platforms.

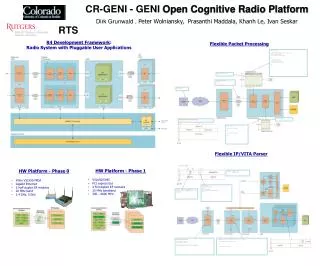

OCRP Application Block • Application Interfaces • System Control : • Application Register map values are provided using Parameter setting options e.g. app_param_valid , app_param_data • Data pointer and size information are provided such that Application Block can fetch data/control information from buffer. • DAC : • Direct access to DAC • Buffer : • App fetches buffer data without intervention from SystemControl. Note that buffer data could be eitherdata or control frame. • Application sub-blocks • OCRP provides a control block and a register map to support the application • The user may or may not use these blocks, (i.e., the User Application may contain its own control logic and its own register map). • User specific logic/functions are contained in the User Application module. The User Application must conform to the interface provided by OCRP

User Application Example: Waveform Generator • This example uses the application data fetch block and register map provided by OCRP. • The application consists of a sine wave generator, an additive white gaussian noise generator and a modulator. One of these blocks can be selected by sending a control command to the system. • Data can be sent to the modulator by a Data Command.

OCRP Library Outline • Libraries : • Common • DAC I/F • ADC I/F • SPI • Register Map • … • Communication • Modulator/Demodulator • Encoder/Decoder • Interleaver/Deinterleaver • OFDM • Frequency Offset Estimation • Frequency Offset Correction • Timing Synchronization • Cyclic Prefix insertion • … • … • DSP • AWGN Generator • Sine Generator • DFT/FFT • FIR/IIR Filter • … • Networking • Ethernet • PCIe • RS232 • … • Processor • uP e.g. Microblaze • Bus e.g. PLB • Bus interface e.g. IPIF • RAM/FLASH interfaces • … • Xilinx • RAM/ROM/FIFO • DCM/PLL • … • Board Specific • Board specific modules which cannot be shared across multiple projects.

OCRP Library Outline (cont’d) • Project Specific • Project specific modules, example : OCRP framework, top level module. • Project specific application module, including register map definition, example : OCRP application module with specific register map definition. • Project specific User Application module, example : OCRP waveform generator. • Note : any modules which can be shared across projects shall NOT be under Project Specific library, but should be propagated to upper libraries such as COMMON, COMMUNICATION and so forth…

OCRP Tx Architecture wibo_sen Wibo SPI wibo_sclk System Controller wibo_sdata Rx Ethernet Interface Command Descriptor Generator wibo_u2_sen Command FIFO radio_io5 radio_io6 radio_io7 Dibo SPI Memory Control dibo_sclk dibo_sen dibo_sdata Buffer other outputs Application Block DAC Interface tx_sync tx_data other outputs

OCRP Application Block • System Control Interface : • Application Register map values are provided using Parameter setting options e.g. app_param_valid , app_param_data • Data pointer and size information are provided such that Application Block can fetch data/control information from buffer. • DAC Interface: • Direct access to DAC • Buffer Iterface: • App fetches buffer data without intervention from SystemControl. Note that buffer data could be eitherdata or control frame. • The OCRP provides a control block and a register map to support the application • The user may or may not use these blocks, (i.e., the user application may contain its own control logic and its own register map). • The user application must conform to the interface provided by OCRP

User Application Example: Waveform Generator • This example uses the application data fetch block and register map provided by OCRP. • The application consists of a sine wave generator, an additive white gaussian noise generator and a modulator. One of these blocks can be selected by sending a control command to the system. • Data can be sent to the modulator by a data command.