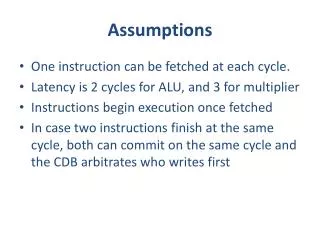

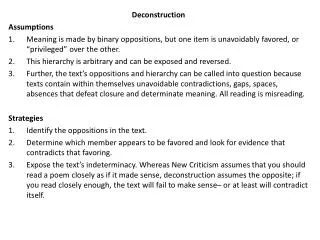

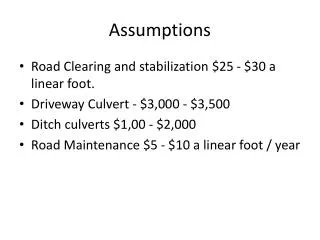

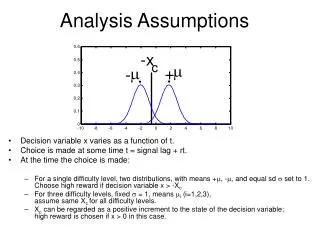

Assumptions

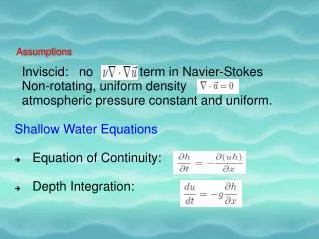

Assumptions. One instruction can be fetched at each cycle. Latency is 2 cycles for ALU, and 3 for multiplier Instructions begin execution once fetched In case two instructions finish at the same cycle, both can commit on the same cycle and the CDB arbitrates who writes first.

Assumptions

E N D

Presentation Transcript

Assumptions • One instruction can be fetched at each cycle. • Latency is 2 cycles for ALU, and 3 for multiplier • Instructions begin execution once fetched • In case two instructions finish at the same cycle, both can commit on the same cycle and the CDB arbitrates who writes first

Multiplier Reservation Stations Instruction Bank Floating Point Registers ALU Reservation Stations Decoder CDB CDB -/+ * CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 1 DecodeI ALU Reservation Stations Decoder CDB CDB -/+ * CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 1 • Obtain Operands ALU Reservation Stations Decoder CDB CDB -/+ * CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 1 Since writing to R2, R2 data is not valid anymore, obtain new data from RS # 4 ALU Reservation Stations Decoder Operands are available, begin execution on next cycle CDB CDB -/+ * CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 2 Since writing to R0, new data is in RS # 1 DecodeJ ALU Reservation Stations Decoder Operands are available, begin execution on next cycle Begin execution CDB CDB -/+ * BUSY Cycle 1 CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 3 K is writing to R2, update the tag to RS#2 DecodeK ALU Reservation Stations Decoder Operands for K not ready, monitor CDB for RS # 1 & 4 CDB CDB -/+ * BUSY Cycle 2 BUSY Cycle 1 CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 4 L is writing to R0, update the tag to RS#5 DecodeL ALU Reservation Stations Decoder Only one operand is ready. Operand 1 will be fetched from RS # 2 CDB CDB -/+ * BUSY Cycle 3 BUSY Cycle 2 CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 5 ALU Reservation Stations Decoder CDB CDB -/+ * Done with I, broadcast results on CDB BUSY Cycle 2 CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 5 ALU Reservation Stations Decoder RS#4 is now free CDB CDB -/+ * Writes results CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 5 ALU Reservation Stations Decoder RS#1 is now free CDB CDB -/+ * Writes results CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 6 ALU Reservation Stations Decoder CDB CDB -/+ * BUSY Cycle 1 CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 7 ALU Reservation Stations Decoder CDB CDB -/+ * BUSY Cycle 2 CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 8 ALU Reservation Stations Decoder CDB CDB -/+ * Writes results CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 8 Write final results to R2. This is valid data; (most recent), and no other WAW ALU Reservation Stations Decoder RS 5, observes a write it has been looking for on the CDB (77.8). Now Multiplier can begin execution on cycle 9 RS#2 is now free CDB CDB -/+ * Writes results CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 9 ALU Reservation Stations Decoder CDB CDB -/+ * Busy, Cycle 1 CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 10 ALU Reservation Stations Decoder CDB CDB -/+ * Busy, Cycle 2 CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 11 ALU Reservation Stations Decoder CDB CDB -/+ * Busy, Cycle 3 CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Cycle 11 Write the values to register 0 ALU Reservation Stations Decoder CDB CDB -/+ * Writes results CDB

Multiplier Reservation Stations Instruction Bank Floating Point Registers Final floating point register values ALU Reservation Stations Decoder CDB CDB -/+ * Writes results CDB