Components & Technologies Implementation…

Components & Technologies Implementation…. ·. ·. SSI/MSI. Bipolar. ·. TTL. Simple PLDs. ECL. ·. Complex PLDs. ·. ·. FPGAs. CMOS. ·. ·. Gate Array. BiCMOS. ·. Std Cell. .. etc. Implementation techniques. Which technology?.

Components & Technologies Implementation…

E N D

Presentation Transcript

· · SSI/MSI Bipolar · TTL Simple PLDs ECL · Complex PLDs · · FPGAs CMOS · · Gate Array BiCMOS · Std Cell .. etc Implementation techniques

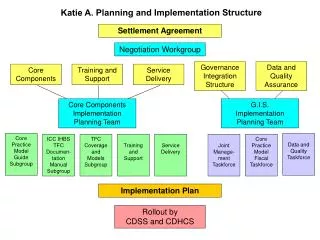

Which technology? • Economic vs. Technical factors… CPLDFPGA Gate Std. Full PLD SSI/MSI array cell custom Semicustom technologies

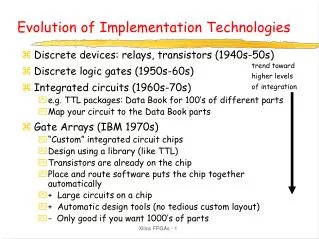

Evolution… ‘standard components’ ‘semicustom components’ 1960 1970 1980 1990 2000 SSI MSI LSI VLSI Gate Array Standard cells Simple PLD CPLD FPGA

SSI/MSI PLD FPGA Gate array Standard cell Full custom Gates/ component 5 .. 100 50 .. 5K 100 .. 10K 500 .. 100K 10K .. 500K 100K .. 10M Cost/gate High Low NRE cost (£) - 1..2K 2..10K 5..50K 10..100K 50..5M Development time (wk) - 1..2 1..2 2..20 5..50 20..200 Comparison of implementation techniques

Comparison (2) Circuit cost as a function of volume Cost Discrete Full custom Volume

Semicustom devices • Mask-programmed devices are ‘customised’ by manufacturer • Gate Array - Gates already fabricated Interconnecting metalisation used to customise design • Standard cell - similar to PCB layout, but using predefined cells More efficient, but requires full mask set

Gate Array and Standard Cell layout I/O pad Logic gate Routing channel A B 1 2 Vdd Gnd 3 4 OUT

Cell layout may be optimised… • As an example, consider a simple D-latch (1) constructed from gates only, and (2) by being able to exploit individual transistor characteristics

Programmable devices • PROM - fixed AND array (decoder) programmable OR array (ROM content) • PLA - both arrays programmable allows p-term sharing • PAL - fixed OR array (so faster, cheaper than PLA…)

Simple PLDs • Basic AND-OR structure with high fan-in(8-12 variables per p-term) • Output macrocells allow multiple output configurations within single package

PAL – most common PLD structure • How beneficial is product sharing? • Not enough to justify the extra AND array • PALs have fixed OR array • Each AND gate is permanently connected to a certain OR gate.

Consider 16L8 • 10 primary inputs • 8 outputs, with 7 ANDs per output • 1 AND for 3-state enable • 6 outputs available as inputs • more inputs, at expense of outputs • Note inversion on outputs • output is complement of sum-of-products

GAL 16V8 • Finally got it right • Each output is programmable as combinational or registered • Also has programmable output polarity

22V10 • More inputs • More product terms • More flexibility

CPLDs vs FPGAs • CPLD architecture • Programmable interconnect between PLDs

FPGAarchitecture • Much larger number of smaller programmable logic blocks • Embedded in a sea of of programmable interconnect

Trends in programmable devices… • Current devices contain more than a million gates • What can we do with them all? • Increasing market in IP to provide standard functions • Manufacturers including dedicated blocks (memory, CPU) plus programmable logic for ‘system-on-chip’ designs

IP functions • May consist of ‘just’ source code or layout too… • MSI building blocks • Maths functions • Memories • Processors • Peripherals • Bus Interfaces • Communications • Networking • EDC/ECC functions • Signal processing • DSP