Motivation

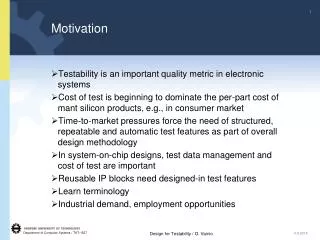

Motivation. Testability is an important quality metric in electronic systems Cost of test is beginning to dominate the per-part cost of mant silicon products, e.g., in consumer market

Motivation

E N D

Presentation Transcript

Motivation • Testability is an important quality metric in electronic systems • Cost of test is beginning to dominate the per-part cost of mant silicon products, e.g., in consumer market • Time-to-market pressures force the need of structured, repeatable and automatic test features as part of overall design methodology • In system-on-chip designs, test data management and cost of test are important • Reusable IP blocks need designed-in test features • Learn terminology • Industrial demand, employment opportunities Design for Testability / O. Vainio

Testing and Diagnosis • Testing: the system is exercised and the response is analyzed to check whether it behaved correctly • Diagnosis: if incorrect behavior is detected, locate the cause of misbehavior. - Assumes knowledge of the internal structure of the system Design for Testability / O. Vainio

Main Categories of Tests Logic verification or functionality tests - Done before chip tapeout to verify the functionality of the design Silicon debug - Run on the first batch of chips that return from fabrication - Confirm that the chip operates as intended and help debug any discrepancies - Can be done at full speed, more extensive than logic verification tests - Less visibility inside the chip compared to design phase Design for Testability / O. Vainio

Main Categories of Tests Manufacturing test or Production test - Done on each manufactured chip before shipping to the customer to verify that the silicon is completely intact - Verify that every transistor, gate, and storage element in the chip functions correctly Design for Testability / O. Vainio

Yield • Not all die on a wafer function correctly • There may be bridged connections or missing features due to dust particles, imperfections in materials or photomasking, etc. • Imperfections may result in a fault • Yield is the number of good die divided by the total number of die per wafer • The goal of a manufacturing test procedure is to determine which die are good and should be shipped to customers Design for Testability / O. Vainio

Cost of Detecting a Fault Wafer: $0.01 - $0.1 Packaged chip: $0.1 - $1 Board: $1 - $10 System: $10 - $100 Field: $100 - $1000 Design for Testability / O. Vainio

Exhaustive testing n Combinational logic Design for Testability / O. Vainio

clk reg m m Combinational logic n Example: n = 25 m = 50 Test takes 1 ms per pattern Design for Testability / O. Vainio

Basic Digital Debugging • When a chip returns from fabrication, the first tests are run in a lab environment • Need a circuit board with features to support testing: - Power for the IC with ability to vary VDD and measure power dissipation - Analog and digital inputs and outputs as required - Clock inputs as required - A digital interface to a PC - Zero insertion force socket for the chip Design for Testability / O. Vainio

The chip should have a serial UART port or some other interface that can be used independently of the normal operation of the chip • Software should provide for peeking (reading) and poking (writing) registers in the chip • Also an interface for a logic analyzer may be provided Design for Testability / O. Vainio

Initial Steps in Chip Testing • ”Smoke test”: ramp up supply voltages from zero without clocks running and monitor the current. • Enable the clocks, some dynamic current should be evident. If possible, initially use reduced clock speed. • Examine various registers using PC-based peek and poke software, checks the integrity of the interface. • The chip may have built-in self test that can be activated over a boundary scan interface. • Otherwise, the functionality is checked from the bottom-up. • Top-level test like running a piece of code at once often does not work, usually because of problems with the test fixture. Design for Testability / O. Vainio

Testers and Test Fixtures • A tester is a device that can apply a sequence of stimuli to a chip or system under test and monitor and/or record the results • Four general types of test fixtures are: - A probe card to test wafers or unpackaged dies - A load board to test a packaged part - A PCB for bench-level testing (with or without tester) - A PCB with the chip in situ, demonstrating the application for which the chip is used Design for Testability / O. Vainio

Handlers • An IC handler feeds ICs to a test fixture attached to a tester. • Devices are gravity-fed to a handler, which mechanically picks the chips up and places them in the test socket on the load board. • The tester stimulus is then applied and chips are binned depending on whether or not they passed the test. Design for Testability / O. Vainio

Shmooing • The ability to vary the voltage and timing on a per-pin basis with a tester allows a process called ”Shmooing”. • For instance, vary VDD from 3 V to 6 V while varying the tester cycle time. • A shmoo plot shows the sensitivity of the part with respect to voltage. • Another example of shmoo is to skew the timing on inputs with respect to clock to look for setup and hold variations. Design for Testability / O. Vainio

Shmoo plot 1.0 * * * * * * 1.1 * * * * * 1.2 * * * * 1.3 * * * 1.4 * * 1.5 * 1.0 1.1 1.2 1.3 1.4 1.5 voltage Normal, well-behaved shmoo Typical speedpath Clock Period in ns * indicates failure Design for Testability / O. Vainio

Shmoo plot 1.0 * * * 1.1 * * * 1.2 * * * 1.3 * * * 1.4 * * * 1.5 * * * 1.0 1.1 1.2 1.3 1.4 1.5 voltage ”Brick wall” Bistable initialization Clock Period in ns Design for Testability / O. Vainio

Shmoo plot 1.0 * * * 1.1 * * * 1.2 * * * 1.3 * * * 1.4 * * * 1.5 * * * 1.0 1.1 1.2 1.3 1.4 1.5 voltage ”Wall” Fails at a certain voltage (coupling, charge sharing, races) Clock Period in ns Design for Testability / O. Vainio

Shmoo plot 1.0 * * * * * 1.1 * * * * 1.2 * * * 1.3 * * 1.4 * 1.5 * 1.0 1.1 1.2 1.3 1.4 1.5 voltage ”Reverse speedpath” Leakage Clock Period in ns Design for Testability / O. Vainio

Shmoo plot 1.0 1.1 1.2 1.3 1.4 * * * * * * 1.5 * * * * * * 1.0 1.1 1.2 1.3 1.4 1.5 voltage ”Floor” Works at high but not low frequency (leakage) Clock Period in ns Design for Testability / O. Vainio

Shmoo plot 1.0 1.1 1.2 * * * * 1.3 * * 1.4 1.5 1.0 1.1 1.2 1.3 1.4 1.5 voltage ”Finger” Coupling Clock Period in ns Design for Testability / O. Vainio