Memory Management

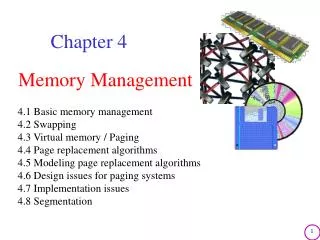

Memory Management. CS 470 - Spring 2002. Overview. Partitioning, Segmentation, and Paging External versus Internal Fragmentation Logical to Physical Address Mapping Placement Algorithms First Fit, Next Fit, and Best Fit Buddy System Intel X86 Memory Mapping Mechanisms

Memory Management

E N D

Presentation Transcript

Memory Management CS 470 - Spring 2002

Overview • Partitioning, Segmentation, and Paging • External versus Internal Fragmentation • Logical to Physical Address Mapping • Placement Algorithms • First Fit, Next Fit, and Best Fit • Buddy System • Intel X86 Memory Mapping Mechanisms • Linking and loading executables

Memory Partitioning • Fixed Partitions (IBM OS/MFT) • Equal Partition Sizes • Variable but fixed Partition Sizes • Internal Fragmentation • Dynamic Partitions (IBM OS/MVT) • External Fragmentation • Need for Compaction

Segmentation versus Paging • Segmentation - Each process divided into variable sized programmer visible segments. External fragmentation. • Paging - Main memory divided into equal sized programmer invisible pages. Trivial internal fragmentation. • Simple (whole process loaded) versus Virtual (parts of processes loaded)

Relocation Segment or Partition Descriptor Base Address Segment or Partition Size Offset Logical to Physical Translation: Size Offset Size Address Exception Base Addr + Offset Physical Address

Logical vs. Physical Addresses • Allows processes to be physically scattered throughout memory while logically contiguous - i.e. programmer thinks it is all one contiguous block of memory • Allows for physical movement without logical movement • Allows processes to occupy same logical addresses.

Logical to Physical AddressTranslation Logical Address Page/Segment Offset 000002 012345 512 4124000 0 4096 4129000 1 Process Page or Segment Table 102400 2010000 2 2022345 8192 7212300 3 Physical Address Base Address Segment Length

Inverted Page Table Logical Address Used in MacOS Page/Segment Offset 000612 012345 hash 512 4124000 2 409 4129000 -1 612 2010000 -1 2022345 27 7212300 1 Hash table Physical Address Page Nbr Base Addr Link

Placement Algorithms • Trivial for allocating blocks of fixed size • Given list of free blocks/partitions and their lengths • First fit -- use first block of sufficient size • Next fit -- use first block of sufficient size after the one that was last allocated • Best fit -- use block whose size is smallest amongst those of sufficient size.

Amount of Fragmentation • First fit is easiest and causes least fragmentation • Next fit requires remembered state and fragments more because all blocks have equal chance to be allocated • Best fit takes longest and almost guarantees lots of small fragments • Can reduce external fragmentation if use only multiples of minimal sized block.

Buddy System • Uses blocks of fixed sizes 2i for L i U to reduce fragmentation • i_List of free blocks of size 2i, L i U . • If request is of size k where 2i-1 k 2i , allocate block of size 2i . • If none of size 2i , divide block of size 2i+1 into 2 equal buddies - repeat recursively. • Coalesce buddies recursively when freed.

Address of Buddy • Assume original block of size 2U is at address which is even multiple of 2U • All blocks of size 2i are at address Addr satisfying ( Addr & (2i - 1)) == 0. • Address of buddy obtained by inverting the ith bit. The buddy is at address: ( Addr & ~ 2i ) | ((~Addr) & 2i )

Buddy Memory Allocation Free Lists 0 12 0 11 0 0 10 9 9 9 8 9 0 7 0 6 10 12 5

Buddy System Blocks Free Block Allocated Block Allocator Return Value Log2N: 0 Log2N: 5 - 12 Forward Link Data Space (N - 4 bytes) Back Link N - 12 Bytes

Intel X86 Memory Mapping • Supports both segmentation and paging • 16 bit segment selector • 13 bit segment number • Descriptor Tables: 0 = Global, 1 = Local • 2 bit requested privilege level • 32 bit segment offset • 64 terabyte address space for each process • Registers (GDTR, LDTR) point to descriptor tables and give their length

Logical to Linear Mapping 3 2 0 31 0 15 Seg Number RPL Segment Offset Seg Desc. 31 22 12 0 Dir Page Offset Descriptor Table Linear Address

Linear to Physical Mapping Linear Address Physical Address 31 0 31 22 12 0 Physical Address Dir Page Offset Page Table Page Directory Dir Entry. Pg TblEntry. CR3

Page/Directory Table Entry 31 12 9 8 7 6 5 4 3 2 1 0 Page Frame Addr G L L D A C D W T U S R W V V Valid R/W Read / Write U/S User / Supervisor W/T Write through C/D Cache Disabled A Accessed D Dirty L Large page GL Global

Translation Lookaside Buffers • Caches page table entries • Separate TLB for each cache • For Data cache, TLB depends on page size • 4 way associative with 16 sets for 4K pages • 4 way associative with 2 sets for 4MB pages • For Code cache, TLB is 4 way associative with 8 sets

Linking and Loading Module 1 Load Module Module 1 Module 2 Loader Module 3 Module 2 Library 1 Library 2 Module 3 Loaded Program Linker Library 1 Memory Library 2

When to resolve addresses • Load Module Types • Absolute load modules • Relocatable load modules • Dynamic Run-time load modules • Address Resolution Times • Programming time • Compile or assembly time • Load module creation time • Load time • Run time

Dynamic Linking • Run time references to routines in external modules causes loading of that module and resolution of the reference • Advantages • Upgrade of libraries can occur without relinking all the applications • Automatic sharing of libraries • Complicates design and testing of applications