Electrostatic Discharge

Electrostatic Discharge. 靜電放電. 靜電放電 ( Electrostatic Discharge, ESD). 造成大多數的電子元件或電子系統受到過度電性應力破壞的主要因素。這種破壞會導致半導體元件以及電腦系統等,形成一種永久性的毀壞,因而影響 積體電路的電路功能,而使 得電子產品工作不正常 。 多是由於人為因素所形成,電子元件或系統在製造、生產、組裝、測試、存放、搬運等的過程中,靜電會累積在人體、儀器、儲放設備等之中。

Electrostatic Discharge

E N D

Presentation Transcript

靜電放電(Electrostatic Discharge, ESD) • 造成大多數的電子元件或電子系統受到過度電性應力破壞的主要因素。這種破壞會導致半導體元件以及電腦系統等,形成一種永久性的毀壞,因而影響 積體電路的電路功能,而使 得電子產品工作不正常。 • 多是由於人為因素所形成,電子元件或系統在製造、生產、組裝、測試、存放、搬運等的過程中,靜電會累積在人體、儀器、儲放設備等之中。 • 加強工作場所對靜電累積的控制,在電子產品中加入具有靜電放電破壞的裝置。可加強積體電路本身對靜電放電的耐受能力上著手,可以解決晶片包裝後,組裝、測試、存放、搬運等所遭遇到大多數靜電放電的問題。

製程的演進 • 在CMOS積體電路中,隨著量產製程的演進,元件的尺寸縮減到深次微米階段,以增進積體電路(IC)的性能及運算速度,以降低每顆晶片的製造成本。但隨著元件尺寸的縮減,卻出現可靠度的問題。 • 在次微米技術中,為了克服所謂熱載子(Hot-Carrier)問題而發展出LDD(Lightly-Doped Drain)製程與結構。 • 為了降低 CMOS元件汲極(drain)與源極(source)的寄生電阻(sheet resistance) Rs 與 Rd,而發展出Silicide製程。 • 為了降低 CMOS 元件閘級的寄生電阻 Rg,而發展出 Polycide 製程。 • 更進步的製程中把Silicide 與 Polycide 一起製造,而發展出所謂Salicide 製程。

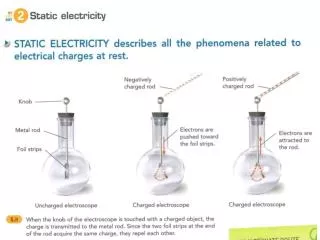

ESD產生的種類 • 人體放電模式 (Human-Body Model, HBM) • 機器放電模式 (Machine Model, MM) • 元件充電模式 (Charged-Device Model, CDM) • 電場感應模式 (Field-Induced Model, FIM)

防護電路設計概念 • 靜電放電防護電路(ESD protection circuits)是積體電路上專門用來做靜電放電防護之用,此靜電放電防護電路提供了ESD電流路徑,以免ESD放電時,靜電電流流入IC內部電路而造成損傷。 • 人體放電模式(HBM)與機器放電模式(MM)之ESD來自外界,所以ESD防護電路都是做在銲墊PAD的旁邊。因CMOS積體電路的輸入PAD一般都是連接到MOS元件的閘極(gate),閘極氧化層是容易被ESD所打穿,因此在輸入PAD的旁邊會做一組ESD防護電路來保護輸入級的元件。 • 在VDD pad與VSS pad的旁邊也要做ESD防護電路,因為VDD與VSS腳之間也可能遭受ESD的放電。 • 靜電放電在是藉由Input到VSS以及VDD與VSS之間的ESD防護電路來旁通ESD電流。

較差的靜電防護設計 • 尤其是在 Input pad,其ESD防護電路只安排在Input pad與VSS之間,Input pad到VDD之間沒有安排ESD防護電路,ESD放電發生時,此負的ESD電壓會先經由Input到VSS之間的ESD防護電路跑到VSS電源線上,沿著VSS電源線流向VDD與VSS之間的ESD防護電路,再經由此VDD與VSS之間的ESD防護電路轉到VDD電源線上,最後由VDD pad流出此IC。 • 靜電放電在是藉由Input到VSS以及VDD與VSS之間的ESD防護電路來旁通ESD電流。有些人做到了Input到VSS之間的ESD防謢電路,卻忘了加上VDD與VSS之間的ESD防護電路,這時在測試之下,積體電路的內部電路常常先被ESD放電電流所損壞,但是在Input pad上的ESD防護電路確毫髮未傷。

靜電電路注意事項 • 隨著晶片的尺寸越大,整個晶片的VDD與VSS電源線也越拉越長,寄生的電容電阻效應便會顯現出來,當IC的佈局造成電源線的雜散電容電阻效應,這些雜散電阻電容會延遲ESD電流經由VDD與VSS之間的ESD防護電路。這時,來不及渲洩的ESD電流便會藉著電源線的而進入到IC內部電路中,因此IC內部電路更易被此種ESD電流所損傷。因此,會造成異常的ESD損傷現象,也就是在I/O pad上的ESD防護電路都好好的,但內部電路已死得很難看,這種內部損傷是無法從單一輸入腳或輸出腳的變化看得出來的。

元件上的改進方法LVTSCR • LVTSCR(Low -Voltage Triggering SCR,低電壓觸發矽控整流器) • 互補式LVTSCR元件的設計 • 高雜訊免疫力的LVTSCR

LVTSCR • SCR元件就是P-N-P-N四層半導體結構的組成。這個四層結構也就是導致CMOS Latchup(鎖住效應)問題的相同結構。但在ESD防護能力上,能在最小的佈局面積下,提供最高的ESD防護能力。由於N-well具有較低的摻雜濃度,因此其接面崩潰電壓高達30~50V(依製程而定)使得SCR元件在ESD防護設計上需要再加上第二級保護電路。這第二級ESD保護電路的目的在提供ESD防護能力當SCR元件尚未導通之前。因SCR元件要到30V才導通,在ESD電壓尚未昇到30V之前,此SCR元件是關閉的,這時SCR元件所要保護的內部電路可能早就被ESD 電壓所破壞了,因此需要加入第二級保護電路來先保護內部電路在第二級保護電路未被ESD破壞之前,SCR元件能夠被觸發導通來排放ESD電流 。

為了改善SCR元件需要另加第二級ESD保護電路的困擾,LVTSCR元件在SCR元件結構中結合了一個short- channel的NMOS元件,利用一個 NMOS的汲極橫跨做在N-well與P-substrate的接面上,這可以使SCR元件的起始導通電壓下降到等效於short-channel NMOS元件的驟回崩潰電壓 LVTSCR元件的導通乃是利用當其內嵌的short-channel NMOS元件發生驟回崩潰時,引發電流自其汲極流向P-substrate,這會引起電流自N-well流向P-substrate,也因而觸發了SCR元件的導通。為了防止LVTSCR元件在CMOS IC正常工作情形下會被導通,其內含的short-channel NMOS元件之閘極(gate)必須要連接到地去,以保持該NMOS元件是關閉的。

互補式LVTSCR設計 • 互補式LVTSCR的靜電放電防護電路。在該電路中,有兩個LVTSCR元件,其中LVTSCR2被安排在PAD到VSS之間用來防護PS-mode的ESD放電,此LVTSCR2是在SCR元件中內嵌一NMOS元件而成的;另外有一LVTSCR1元件被安排在PAD到VDD之間,用來防護ND-mode的ESD放電,此LVTSCR1元件是在SCR元件內嵌一PMOS元件而成的。這LVTSCR1與LVTSCR2正好形成互補式的的結構,可以有效地提昇該PAD的ESD防護能力。 • 由於LVTSCR1內嵌的PMOS之閘極是接到VDD,所以LVTSCR1在CMOS IC正常工作情形下是關閉的,只有當ESD放電時才會被導通,此LVTSCR1的導通電壓等效於PMOS元件的驟回崩潰電壓(約-10~-15V)。LVTSCR2元件就是6.3.1所說的LVTSCR元件一樣,在此不再重覆。圖6.3-4顯示把這個互補式LVTSCR靜電放電防護電路實現出來的元件剖面圖,利用這種特殊設計,CMOS IC的ESD耐壓度可以有效地提昇而不需要動用額外的ESD- Implant或Silicided-diffusion Blocking的額外製程處理。該互補式LVTSCR靜電放電防護電路在IC佈局上的實施

此互補式LVTSCR靜電放電防護電路也可以與CMOS輸出級的電晶體元件合併佈局在output PAD的旁邊,用來保護該CMOS輸出級的電晶體元件,在圖的PTLSCR (PMOS-TriggerLateral SCR)元件就等效於圖中的LVTSCR1元件。NTLSCR(NMOS-Trigger Lateral SCR)元件就等效於圖中的LVTSCR2元件。顯示出其互補式的特性,該PTLSCR元件可與輸出級的輸出PMOS在佈局上結合在一起共用防護圈(guard rings),NTLSCR元件可與輸出級的輸出NMOS在佈局上結合在一起共用防護圈,所以佈局面積可以更有效地節省,而在深次微米製程下輸出級的ESD防護能力得以提昇。

高雜訊免疫力的LVTSCR元件 • 隨著積體電路的廣泛應用,積體電路可能被使用在具有雜訊干擾的工作環境下,積體電路必須對外界雜訊干擾具有某種程度的免疫能力。突發的雜訊干擾可能會觸發在 I/O Pad上的LVTSCR元件導通而造成電路系統工作上的錯誤。 • 實際的例子顯示在圖中,一積體電路Chip 1的輸出級推動另一積體電路Chip 2的輸入級,該積體電路Chip 2的輸入級是用一LVTSCR元件來做靜電放電的防護元件

高電流低電壓NMOS觸發之橫向矽控整流器(high-current NMOS-trigger lateral SCR)元件結構圖,叫做 HINTSCR 元件。 • 高電流低電壓PMOS觸發之橫向矽控整流器(high-current PMOS-trigger lateral SCR)元件結構圖,叫做 HIPTSCR 元件。

輸入腳/輸出腳的ESD 輸入腳ND模式之ESD放電造成IC內部損傷的示意圖。

VDD與VSS間的寄生元件 • ESD電壓跨在VDD與VSS電源線之間,除了會造成IC 內部電路損傷之外,也常會觸發一些寄生的半導體元件導通而燒毀。在CMOS IC中,最常發生燒毀現象的寄生元件 就是p-n-p-n的SCR元件及n-p-n的橫向雙載子電晶體(BJT)。隨著製程的先進,寄生元件間的間距也越來越小,這使得 該寄生的元件具有更高的增益(Gain)及更易被觸發的特性

改善措施 • NMOS元件加上串聯電阻以提昇ESD電流承受能力的美國專利設計

靜電放電防護設計之案例探討 • ESD防護設計隨著積體電路的各式各樣應用而會有不同的設計出現。但在深次微米CMOS製程技術下,越來越嚴重的ESD問題是元件充電模式(CDM)之靜電放電現象。 • 由於輸入的閘極氧化層(gate oxide)在0.25μm製程下,僅約50A厚度而已,如此薄的閘極氧化層對CDM的靜電放電非常敏感

動態浮接閘級 之ESD防護技術在小輸出電流規格之輸出驅動級的設計

利用『動態浮接閘級技術』 之整個輸出驅動級電路在 0.35-μm製程下的佈局實例