第二章 数字交换和数字交换网络

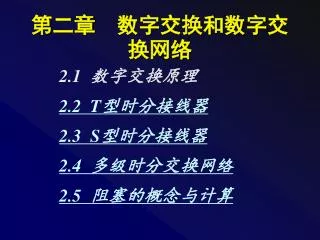

第二章 数字交换和数字交换网络. 2.1 数字交换原理 2.2 T 型时分接线器 2.3 S 型时分接线器 2.4 多级时分交换网络 2.5 阻塞的概念与计算. 2.1 数字交换原理. 2.1.1 数字交换 程控数字交换机的根本任务是通过数字交换来实现任意两个用户之间的语音交换,即在这两个用户之间建立一条数字话音通道。. 最简单的数字交换方法是给这两个要求通话的用户之间分配一个公共时隙(时分通路),两个用户的模拟话音信号经数字化后都进入这个特定的时隙( Time Slot,TS), 这就是动态分配时隙的方法。 2.1.2 时隙交换原理

第二章 数字交换和数字交换网络

E N D

Presentation Transcript

第二章 数字交换和数字交换网络 • 2.1 数字交换原理 • 2.2 T型时分接线器 • 2.3 S型时分接线器 • 2.4 多级时分交换网络 • 2.5 阻塞的概念与计算

2.1 数字交换原理 • 2.1.1 数字交换 • 程控数字交换机的根本任务是通过数字交换来实现任意两个用户之间的语音交换,即在这两个用户之间建立一条数字话音通道。

最简单的数字交换方法是给这两个要求通话的用户之间分配一个公共时隙(时分通路),两个用户的模拟话音信号经数字化后都进入这个特定的时隙(Time Slot,TS),这就是动态分配时隙的方法。 • 2.1.2 时隙交换原理 • 时序开关K入和K出每秒旋转8000周,每周所需时间是125s。

在TS1时隙时,K入和K出分别与接点1#入和2#出相连,即K入和1#存储单元相连,K出与2#存储单元输出相连,此时在TS1时隙里传送来的a话音信息就存入话音存储器的1#单元,而话音存储器的2#单元内存放的b话音信息就在此时通过K出的1#接点送出,也就是输出端在TS1时隙送出b话音信息给TS1用户。 在TS1时隙时,K入和K出分别与接点1#入和2#出相连,即K入和1#存储单元相连,K出与2#存储单元输出相连,此时在TS1时隙里传送来的a话音信息就存入话音存储器的1#单元,而话音存储器的2#单元内存放的b话音信息就在此时通过K出的1#接点送出,也就是输出端在TS1时隙送出b话音信息给TS1用户。 • 2.1.3 数字交换网络

2.2 T型时分接线器 • 2.2.1 T接线器的基本组成 • T型时分接线器(Time Switch)又称时间型接线器,简称T接线器。它由话音存储器(Speech Memory,SM)和控制存储器(Control Memory,CM)两部分组成,其功能是进行时隙交换,完成同一母线不同时隙的信息交换,即把某一时分复用线中的某一时隙的信息交换至另一时隙。

话音存储器(SM)用于暂存经过PCM编码的数字化话音信息,由随机存取存储器(Random Access Memory,RAM)构成。 • 控制存储器(CM)也由RAM构成,用于控制话音存储器信息的写入或读出。 • 话音存储器存储的是话音信息,控制存储器存储的是话音存储器的地址。

2.2.2 T接线器的工作原理 • 一、读出控制方式 • 读出控制方式的T接线器是顺序写入控制读出的,如图2.3所示,它的话音存储器SM的写入是在定时脉冲控制下顺序写入,其读出是受控制存储器的控制读出的。

话音存储器中每个存储单元内存入的是发话人的话音信息编码,通常是8位编码。 话音存储器中每个存储单元内存入的是发话人的话音信息编码,通常是8位编码。 • T接线器的工作是在中央处理机的控制下进行。当中央处理机得知用户的要求(拨号号码)后,首先通过用户的忙闲表,查被叫是否空闲,若空闲,就置忙,占用这条链路。中央处理机CPU根据用户要求,向控制存储器发出“写”命令,将控制信息写入控制存储器。

用户B的回话信息b如何传送,也要由中央处理机控制,向控制存储器下达“写”命令,令其在1#单元中写入“8”。 用户B的回话信息b如何传送,也要由中央处理机控制,向控制存储器下达“写”命令,令其在1#单元中写入“8”。 • 二、写入控制方式 • T接线器采用写入控制方式时,如图2.4所示,它的话音存储器SM的写入受控制存储器控制,它的读出则是在定时脉冲的控制下顺序读出。

当中央处理机(Central Processing Unit,CPU)得知用户要求后,即向控制存储器下“写”令,命令在控制存储器的1#单元写入“8”,在8#单元写入“1”。

2.2.3 T接线器的电路组成 • 时分接线器的交换容量主要取决于组成该接线器的存储器容量和速度,多以8端或16端PCM交换来构成一个交换单元,每一条PCM线称HW(Highway)。 • 图2.5是8端脉码输入的T接线器方框图,由复用器、话音存储器(SM)、控制存储器(CM)和分路器所组成。

一、复用器 • 复用器的基本功能是串/并变换和并路复用。其目的是减低数据传输速率,便于半导体存储器件的存储和取出操作;尽可能利用半导体器件的高速特性,使在每条数字通道中能够传送更多的信息,提高数字通道的利用率。

1.串行码和并行码 • 如图2.7(a)所示,串行码是指各时隙内的8位码D0~D7是按时间的顺序依次排列。 • 如图2.7(b)所示,并行码是指各时隙内的8位码D0,D1,…,D7分别同时出现在8条线上。

每一端的脉码传输速率是2.048Mbit/s,若8端PCM脉码输入以串行传输时,其传输速率将达到16.384Mbit/s,若16端输入时,其传输速率将达到32.768Mbit/s,这样高的传输速率会带来许多问题。 每一端的脉码传输速率是2.048Mbit/s,若8端PCM脉码输入以串行传输时,其传输速率将达到16.384Mbit/s,若16端输入时,其传输速率将达到32.768Mbit/s,这样高的传输速率会带来许多问题。 • 2.控制时序 • 8端PCM脉码输入的256个时隙排列方式应是HW0的TS0,HW1的TS0,HW2的 TS0,…,HW7的TS0;HW0的TS1,HW1的TS1,HW2的TS1,…,HW7的TS1等等。

3.串/并变换 • 在图2.6所示的复用器中,每一条HW接一个移位寄存器,移位寄存器的输入端为一条线,线上传输的是32个时隙的串行码。 • 4.并路复用 • 在图2.6所示的复用器中,8选1的电子选择器的功能是把8个HW的并行码按一定的次序进行排列,一个一个地送出。

二、分路器 • 分路器由锁存器和移位寄存器组成,如图2.9所示。其功能与复用器正好相反,完成并/串变换和分路输出功能。

三、话音存储器 • 话音存储器由RAM组成,是暂存话音信息编码的存储设备。图2.10所示为读出控制方式的话音存储器的原理方框图。话音存储器的写入受定时脉冲控制(顺序写入),读出是由控制存储器读出数据B0~B7控制进行。

四、控制存储器 • 控制存储器是由RAM、锁存器、比较器和读写控制器组成,图2.11所示为具有256个存储单元的控制存储器,所以由8个二进制数据码A0~A7分别表示256个单元地址。A0~A7是定时脉冲。

2.3 S型时分接线器 • S型时分接线器是空间型接线器(space switch),其功能是完成“空间交换”。即在一根入线中,可以选择任何一根出线与之连通。

2.3.1 S型接线器的基本组成 • S型接线器由m×n交叉点矩阵和控制存储器组成。在每条入线i和出线j之间都有一个交叉点Kij,当某个交叉点在控制存储器控制下接通时,相应的入线即可与相应的出线相连,但必须建立在一定时隙的基础上。

2.3.2 S型接线器的工作原理 • 根据控制存储器是控制输出线上交叉接点闭合还是控制输入线上交叉接点的闭合,可分为输出控制方式和输入控制方式两种。 • 一、输出控制方式 • 图2.13所示为8×8 S型时分接线器的组成方框图。

二、输入控制方式 • 输入控制方式的S型时分接线器,每条输入线上都配有一个控制存储器,控制该输入线与输出线的所有交叉接点。

2.4 多级时分交换网络 • 2.4.1 T-S-T型时分交换网络 • 一、读—写方式的T-S-T网络 • T-S-T交换网络是由输入级T接线器(TA)和输出级T接线器(TB),中间接有S型时分接线器组成。

1.奇偶关系 • 2.相差半帧的关系——反相法 • 二、写—读方式的T-S-T交换网络

三、T-S-T交换网络的分析 • 1.输入级T接线器和输出级T接线器的安排 • 从原理上讲,输入T级和输出T级采用何种控制方式都是可以的,但是从控制的方便,以及维护管理的角度出发,还是有讨论的必要。 • 2.控制存储器的合用 • 由于输入T级和输出T级采用了不同的控制方式,故它们的存储器可以合用。

(1)读—写方式的合用 • 从图2.15可以看出,CMA0和CMB0两个控制存储器,一个是在2#单元里存24#地址,一个是在130#单元里存24#地址,这说明两者合用后,只要在相差半帧(或相差一个时隙)的单元地址里写入同样的话音在SM的存放地址就可以了。

(2)写—读方式的合用 • 从图2.16可以看出,CMA0和CMB0占用的单元地址是相同的,都是24#单元,只是单元里存放的话音存储器的地址相差半帧。

2.4.2 S-T-S型时分交换网络 • S-T-S三级时分交换网络是由输入S级、中间T级和输出S级组成,如图2.19所示。 • 2.4.3 其他形式的多级时分交换网络 • 一、T-S-S-T 网络 • 日本NEC公司生产的NEAX-61是典型的T-S-S-T时分交换网络结构。

二、S-S-T-S-S网络 • S-S-T-S-S是意大利Telettra公司的DTN-1数字交换机的交换网络所采用的结构,这种网络是在两侧各配备两级S型接线器,中间为一级T型接线器。

2.5 阻塞的概念与计算 • 2.5.1 阻塞的概念 • 所谓阻塞是指主叫向被叫发出呼叫时,被叫虽然空闲,但由于网络内部链路不通,而使呼叫损失的情况。

2.5.2 阻塞概率的计算 • 以图2.15的T-S-T网络为例,这是一个具有16条输入母线,16条输出母线,每条母线上有256时隙的交换网络。 • 为了降低阻塞概率,就需要增加级间的链路数即内部时隙数。 • 这样低的阻塞概率可以近似地看作为零,即交换网络可认为是无阻塞网络。