简易数字存储示波器设计

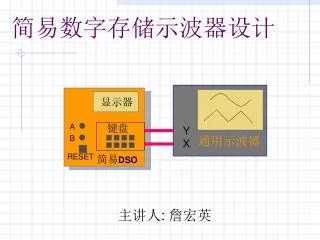

A. B. RESET. 简易数字存储示波器设计. 显示器. 键盘. Y X. 通用示波器. 简易 DSO. 主讲人 : 詹宏英. 有关现代显示技术. 扫描显示 光栅显示 点阵显示. 本赛题是 : CRT 扫描显示 电子测量的一种典型技术. 赛题任务书. 一 任务 : 设计一简易数字存储示波器 ( 简易 DSO ). (1) 信号频率: DC~50kHz , Ri>100k Ω ; (2) 垂直: 32 级 /div , 水平 20 点 /div ,

简易数字存储示波器设计

E N D

Presentation Transcript

A B RESET 简易数字存储示波器设计 显示器 键盘 Y X 通用示波器 简易DSO 主讲人: 詹宏英

有关现代显示技术 扫描显示 光栅显示 点阵显示 本赛题是: CRT扫描显示 电子测量的一种典型技术

赛题任务书 一 任务:设计一简易数字存储示波器 ( 简易DSO )

(1) 信号频率: DC~50kHz, Ri>100kΩ; (2) 垂直: 32级/div, 水平20点/div, 屏幕面积 8×10 div2 ; (3) 垂直灵敏度:0.1V/div,1V/div,误差≤5% ; (4) 水平扫速: 0.2s/div,0.2ms/div,20μs/div, 误差≤5%; (5) 单次触发、扩展、内触发、上升沿、电平可调; (6) 显示波形无明显失真。 赛题任务书 二 要求 1. 基本要求

赛题任务书 赛题任务书——要求 2. 发挥部分 (1)连续触发存储方式,并有“锁存功能”; (2)双踪显示; (3)水平移动扩展 一倍; (4)垂直灵敏度 0.01V/div,低输入噪声电压。

简易数字存储示波器设计 (解析) 主要内容: * 对赛题要求的分析 * 方案讨论 * 部分电路设计及模拟 * 安装调试 * 测试结果 * 小结 * 展望

1. 对赛题要求的分析 (1) 工作流程:采集、存储、显示。 具有:A/D、RAM、D/A等主要器件; (2) 内触发上升沿、触发电平可调; 扫描速度 0.2s/div,0.2ms/div,20 μ s/div; 垂直灵敏度0.1V/div, 1V/div, 0.01V/div, 连续、移动扩展、双踪。 要具有控制功能 1.控制器 2. 人机接口

1. 对赛题要求的分析 (3)简易DSO组成框图 Y通道包括前向通道和后向通道

2. 方案讨论 2.1 采样方式的选择 实时采样和等效时间采样 题中要求信号DC~50kHz,样点直接恢复方式为20点/周期,采速高达1000kHz(1 μ s),A/D转换速率1Ms/s 采用实时采样方式

2. 方案讨论 2.2 控制器的选择 * 对控制器的要求 采集速率: 高达1000kHz(1 μ s), 低至 20ms; (决定于扫描速度) 样点恢复速率:10kHz; 程控增益: 1V/div,0.1V/div,0.01V/div 双踪、扩展… * 三种方案 (1) VLSI 例如 CPLD (2) MUC (3) MUC+CPLD

2. 方案讨论 选择方案(3) MUC和CPLD 控制器框图:

2. 方案讨论 2.3 技术指标初步分配(误差是定量指标) (1) 信号通道 前向通道(采集、存储)≤2.5% 后向通道(恢复) ≤2% 2.5% + 2% = 4.5% ≤ 5% (2) 时基(时间基线、扫描速度) 控制信号(采样时钟)误差忽略不计 扫描电压及输出电路 ≤2%

简易DSO划分为3个部分:Y 通道(前、后向通道)、X通道和控制器3.1 前向通道* 作用 (初步构思) 3. 部分电路设计及模拟 S1 校零,S2校满度 * 内容 信号调理电路; 低通滤波器;电平移位; 前向通道通道性能分析;双踪显示;触发电路。

3. 部分电路设计及模拟 1)输入电路 * 要求: Ri’≥100kΩ,输入噪声电压影响; * 输入电阻(阻抗)对被测系统的影响 Z越高,影响越小。

3. 部分电路设计及模拟 * 输入电路 * 取R≥ 100kΩ * 运算放大器LF353 初步核算: 输入电阻 Ri’ =R// Ri ≈ R ≈ 100kΩ; 输入端噪声电压 3.6nV, 而最高灵敏度时的测量分辨力为 312μV, 3.6nV《 312μV

3. 部分电路设计及模拟 2) 信号调理电路 * 作用 使信号符合A/D输入的要求 (预计A/D输入≤2V) * 增益计算 输入幅度 灵敏度×8div 8V, 0.8V, 0.08 增益 0 . 25, 2 . 5, 25 (由程控实现) * 电路图

3. 部分电路设计及模拟 * 有关解释 程控开关Sn 必须是模拟开关,选择集成开关MAX4501; 增益调节电阻Rnn ,模拟开关的内阻计人其中; 补偿电容 改善通道频响特性

3. 部分电路设计及模拟 3)低通滤波器* 作用:抗混迭 采样信号的频谱混迭现象及改善方法 * 抗混迭滤波器电路

3. 部分电路设计及模拟 * 有关解释 运算放大器构成有源低通滤波器; 二阶Butterworth低通滤波器.

3. 部分电路设计及模拟 4)电平移位电路 假设A/D要求+极性输入电压,而此前电路输出±极性电压。 5)前向通道性能分析 * 目的:阶段性小结 * 内容:频率特性的模拟; 元器件参数的影响; 环境温度的影响。

3. 部分电路设计及模拟 前向通道频率特性的模拟(用EWB对程控增益放大器和低通滤波器模拟分析) 结果 -3dB带宽80kHz〉50kHz 满足设计要求

3. 部分电路设计及模拟 6)双踪示波器的实现 * 样点采集次序 交替、断续 考虑最慢采样速率 20ms/点,选择断续方式 * 样点数/页 20点/div × 10div=200点(256) 扩展方式 200 ×2=400点(512) * 电路方案 选择方法二

3. 部分电路设计及模拟 7)触发电路 * 要求: 内触发、正沿、触发电平可以调节; * 电路 说明: 触发信号来自A通道; 采用比较器,比较电平的极性为+、可以调节; 输出为下降沿,向单片机申请中断( )。

3. 部分电路设计及模拟 3.2 信号的采样、量化、存储 (DSO的基本技术) 1) 采样和模数转换器(A/D) A/D的技术要求 (1) 转换速率 20 μ s/div 1μs/点1 Ms/s (2)量化位数32级/div × 8=256级/8div 256=288bit 量化误差 1LSB=1/28 0.4% (3)输入幅度+( 0---2)V 选择:TLC5510

3. 部分电路设计及模拟 关于TLC5510 ① 内含S/H; ② 为半闪烁结构(flash) ,两个4bit并行A/D组合为8 bit 转换速率20 Ms/s; ③ 输入信号 +(0– 2)V; ④ 基准电压 + 2V 等等 TLC5510内部电路结构

3. 部分电路设计及模拟 2) 数据存储器 要求: 存储容量 单踪 512 byte,双踪 1024 byte; 写速率 1 μs/点 ; RAM 或 FIFO或双口RAM。 3)电路方案 双A/D,RAM 实现双踪要求

3. 部分电路设计及模拟 3.3 后向通道 1) 设计要求 将数字信号(RAM中的数据)恢复为模拟信号并作为通用示波器 的Y 输入信号(8V), A、B信号从同一个Y端输入。 要考虑的问题:信号恢复电路及器件选择,同步扫描电压,双 踪显示。 2)信号恢复 采用器件 D/A 恢复速率 选择宜人的观察速率10kHz 100 μs/点 256点× 100 μs/点=25.6 ms (40次/秒) 这样可以免除的高速D/A的要求(是DSO的优点); D/A 选择 DAC0832。

3. 部分电路设计及模拟 3) 同步扫描电压设计 * 同步作用 显示稳定的信号波形 * 同步扫描电压设计 两种产生扫描电压的方法: 通用示波器扫描电压(要同步信号) 简易DSO产生 选择由简易DSO产生

3. 部分电路设计及模拟 * 扫描电压的产生 用D/A产生 D/A选择DAC0832 (与信号恢复器件一致) D/A输入数据为8 bit(00—FF)H递增, (实际为阶梯波而不是斜波) 关于扩展显示的信号恢复 ① 基本思想

3. 部分电路设计及模拟 • 恢复的数据 在两个页面中取连续的256点 • 扫描电压 与前相同 因此,扩展显示是移动地在两个页面中显示一个页面,关键是控制电路和软件。 4)双踪显示 要求:… 问题: A、B两个信号恢复后的显示如图(a)所示,不便于观察。实际要求将A、B两个信号分别显示在通用示波器屏幕的上下方,如图(b)所示,要求进行光迹分离。 光迹分离两种方法: 电平位移;数据处理。

3. 部分电路设计及模拟 5) 数据恢复电路 有关解释:① D/A YA 、D/A YA 和D/A X 分别用于恢复 A、B信号和产生扫描电压 ② A Y和A X为Y和X的输 出电路.③ 在同一地址的A、 B数据分时地进行恢 复,否则两信号的光 迹要重叠。

3. 部分电路设计及模拟 3.4 控制器的设计 控制器的作用 控制、数据处理; 控制器的组成 控制器自身、人机接口。 1) 键盘 性质 矩阵扫描非编码键盘 组成 (8个键)

3. 部分电路设计及模拟 对键盘的解释: (1)按下的键状态为“0”; (2)s/div和V/div为+1键 编码关系见表6.1; (3)默认的仪器工作状态:0.2ms/div 、0.1V/div; (4)扩展移动键每按一次+5; (5)底层控制器(CPLD)扫描键盘,有键按下时向顶底层控制器 (单片机)申请中断( ); (6)仪器的复位键(RESET)不属于键盘管理。

3. 部分电路设计及模拟 3)控制器的硬件设计 (1) DSO的操作时序 键盘输入 (相关设置)启动 等待触发 仪器操作(采集、 存储、数据处理、信号恢复、显示) 见图6.20,例如

3. 部分电路设计及模拟 种类 用途 来源 静 态 信 号 校零 输入短路 CPLD 校满度 输入端接0.8V CPLD 程控增益和扫描速度 分别接通增益和选择时钟 CPLD 动 态 信 号 开始写数据 RAMa和RAMb地址为 00H CPLD 停止写数据 RAMa和RAMb地址为 FFH 或1FFH CPLD 数据处理 将零点偏移、满度校准以及光迹分离量计入采集数据 单片机和CPLD 启动显示 从RAM读数据至D/A 单片机和CPLD 扩展显示 选择数据的起点地址X 单片机和CPLD 锁存显示 不再采集数据,继续显示 单片机和CPLD 双踪显示 A、B信号同时显示 单片机和CPLD 单次触发 只产生一次触发扫描 单片机和CPLD (2) 控制信号

3. 部分电路设计及模拟 (3) 控制器件的选择 MUC AT89C52 CPLD ACEX1K10 AT89C52 8bit 12MHz 、 8kbyte EEPROM 、 256byte RAM ACEX1K10 3.5ns 时钟 I/O EBA(512byte) (可以在线编程) 从存储器的配置来说,如此选择是极其有利的 (4)控制器电路图

3. 部分电路设计及模拟 * 底层控制器电路

3. 部分电路设计及模拟 * 顶层控制器电路

3. 部分电路设计及模拟 * 对控制电路的说明 CPLD部分 ① 两层控制器总线连接(Part A ) 锁存器连接 直接连接 ② 时钟信号产生电路(Part B) 时钟信号种类: 输入 10MHz; 3种采样时钟(由扫选择)和100Hz; 选择时钟的编码自PartD

3. 部分电路设计及模拟 ③数据存储器(Part C) 信号采集时: 数据来自A/D; Reset 开始存储(00H); 写时钟来自PartB。 信号恢复时: 读时钟自单片机; 读允许信号自PartD ; 读出数据经过数据选择器 至单片机。

3. 部分电路设计及模拟 ④ 有关的控制信号(Part D) 锁存器(a) 输出时钟选择码; 锁存器(b) 输出产生扫描电压 的数据; 锁存器(c) 至前向通道控制开关; 缓冲器(d) 传递键值编码 它们的选通由单片机 P1口通过138实现

3. 部分电路设计及模拟 ⑤ 键盘扫描电路(Part E) 扫描时钟100Hz,自Part B; 输出行扫描信号,读入列信号,输 出键值编码,至Part D; 向单片机申请中断 。

3. 部分电路设计及模拟 * 对控制电路的说明 单片机部分 • 显示器是其外设; • 与CPLD 的连接是P0、P1口; • 键盘中断优线于触发中断; • 输出信号恢复和产生扫描电压的数据; • 单片机的有关设定 P1口,表6.4 内RAM的设定,表6.5 前向通道的控制信号,表6.6 补充说明: 扫描速度为0.2s/div时,每采样一点就显示一次,否则要产生 闪烁现象。 4)控制器的软件设计(根据DSO的工作过程编写) 自顶向下,充分利用子程序和中断功能 一个主程序和两个中断子程序

3. 部分电路设计及模拟 向单片机申请中断,再至CPLD的Reset引脚,使其从地址00H开始存储采集的数据.

安装调试 理论设计与实际工作之间; 单元电路和级连电路之间; 电路的实际负载能力。 5 测试结果 5.1 拟定测试方案 方案的组成 对测试仪器的精度要求

5 测试结果 5.2 测试结果记录 (测试项目要针对设计要求) * 单次和连续扫描 * 扩展功能 * 双踪示波 * 垂直灵敏度 * 扫描速度 5.3 测试结果总评价 (误差≤5% 实事求是、中肯)

6 小结 (1) 模拟电路部分设计较合理; (2) 两层控制; (3) 充分利用片内存储器; (4) 充分利用新颖电子技术。 7 展望 (1) 采用程控电阻 (2) 扩展功能的再扩展,利用双扫描和CRT的Z通道 (3) 数字信号处理

电子设计竞赛 是一项千军万马的活动, 让我们在不同的岗位上共同努力!