Advanced Constraint-Based Techniques for Optimizing Embedded System Composition

This document explores innovative methodologies in constraint-based programming for embedded system composition. It combines model-based system design with aspect-oriented (AO) strategies to enhance the efficiency of embedded systems. Key practices include automated specification and application of constraints, facilitating the rapid construction of system variants with minimal cost. It highlights the use of a meta-weaver for the automation of constraint application, ultimately providing traceability from requirements to implementation. The focus on customizable tools and dynamic system behavior paves the way for advanced reconfigurable designs.

Advanced Constraint-Based Techniques for Optimizing Embedded System Composition

E N D

Presentation Transcript

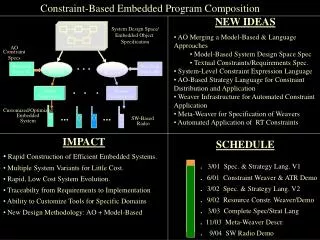

Constraint-Based Embedded Program Composition • NEW IDEAS • AO Merging a Model-Based & Language Approaches • Model-Based System Design Space Spec • Textual Constraints/Requirements Spec. • System-Level Constraint Expression Language • AO-Based Strategy Language for Constraint Distribution and Application • Weaver Infrastructure for Automated Constraint Application • Meta-Weaver for Specification of Weavers • Automated Application of RT Constraints System Design Space/ Embedded Object Specification AO Constraint Specs System SW/HW Description Waveform Descr. #1 Constraint Weaver Constraint Weaver Waveform Descr. #N System Composition System Composition Customized/Optimized Embedded System SW-Based Radio • IMPACT • Rapid Construction of Efficient Embedded Systems. • Multiple System Variants for Little Cost. • Rapid, Low Cost System Evolution. • Traceabilty from Requirements to Implementation • Ability to Customize Tools for Specific Domains • New Design Methodology: AO + Model-Based SCHEDULE .3/01 Spec. & Strategy Lang. V1 .6/01 Constraint Weaver & ATR Demo .3/02 Spec. & Strategy Lang. V2 .9/02 Resource Constr. Weaver/Demo . 3/03 Complete Spec/Strat Lang . 11/03 Meta-Weaver Descr. . 9/04 SW Radio Demo

Constraint-Based Embedded Program Composition Institute for Software Integrated Systems Vanderbilt University PI: Ted Bapty Jeff Gray, Sandeep Neema

Project Goals • Investigate the Interactions between MBS+AO • Extend Existing Model-Based Embedded System Design System • Language-based Constraints, • Strategy Language for Constraint Distribution • Customize the tools for Communications • Demonstrate on Software-Based Radio Application

ATR Adaptive Computing Systems Model-Integrated Design Environment Graphical Model Builder Model Analysis Tools MODELS Multi-Aspect Modeling Environment Behavioral Models Algorithm Models Resource Models System Generation SW HW SW HW Reconfigurable Runtime Environment Simulation Environment

Model-Integrated Design Environment (MIDE) • Design Capture for HW/SW Codesign: Multiple Aspects • Software/Algorithm Data Flow with Multiple Design Alternatives • Hardware Resources: Heterogeneous (DSP,RISC,FPGA) • Dynamic System Behavior: Multi-modal systems • Constraint Specification Language: Link SW/HW/Behavior • Result: Comprehensive, Flexible HW/SW System Model • Analysis of Models (Design) • Design-Space Exploration: • Optimize design, select best configurations from alternative designs • Highly scalable using OBDD • Numerical/Algorithmic Simulation with Matlab • Multiple-Resolution Performance Simulation with Discrete Event Simulator

Model-Integrated Design Environment (MIDE) • HW/SW System Synthesis • Generate Real-Time Schedules • Generate VHDL for FPGA or ASIC • Generate Interconnection Topology/Communication Maps • Generate Reconfiguration Manager Configuration • Result: Functional HW/SW System w/ Dynamic Reconfiguration Capabilities. Compatible with Industry-standard VHDL Compilers • Runtime Support • Microkernel for Heterogeneous Distributed DSP’s • Virtual Hardware Microkernel for FPGA/ASIC • Dynamic System Reconfiguration Controller • Real-Time, reconfiguration support. • Result: Portable, heterogeneous uniform execution environment

Multiple-View Graphical Modeling/Flexible Design Space Behavioral Structural Resource

Modeling ParadigmStructural/Algorithmic Description Model/Object Hierarchy Example Model Primitive Primitive Compound Compound Primitive Primitive Compound Template Primitive Compound Template Compound Software Compound Primitive Hardware Primitive Compound Primitive Primitive

Defining A Design SpaceTemplates for Algorithm Alternatives Long Range Track Algorithm Alternatives Spatial Domain Spectral Domain Sensor Preprocess Filter Preprocess 2D FFT Image DB XCorr Img Spec DB Mult Error Comp Error Comp Guidance Loss of Track

Modeling ParadigmResource Models ObjectHierarchy Network Processor FPGA ASIC Core Ports Core Ports Ports ExampleModel Network Processor Processor ASIC Processor FPGA FPGA

Modeling Paradigm Behavioral Description: Hierarchical State Machine Transition Rules Mode A Mode B Transition Rules Transition Rules Transition Rules Mode C Attributes Algorithms Performance Specs Constraints (Power/Size/User Defined)

Constraint Modeling S1 S2 S3 / e1[S21]/ hierarchical parallel FSM /../ (mode=S2 implies (Proc.Powr<10)) Power Constraints Behavior and Compatibility Constraints Behavior Model /../ (mode!=S3)implies (Pr2.assignees =(P1i or P2j))and(Pr2=Pr2j) (mode=(S1 or S2))implies(P1=P1i)) Resource Constraints P1 P2 Pr2 Pr1 Pr3 P3 hierarchical interconnect alternatives C1 (D1.time - D2.time) < 2 Resource Models Timing Constraints Processing Structure Models

Design Space Exploration Resource Model Binary Encoding BDD Representation Behavior Mod. (Hier. Par. FSM) Binary Encoding BDD Representation Full Symbolic Design Space Structural Mod. (Hier. Altern.) Binary Encoding BDD Representation Pruned Design Space Binary Encoding Constraints (OCL) BDD Representation OBDD Analysis

System Synthesis HOST PC ASIC P1 I/O Interfaces C40 DSP XC4010 FPGA Kernel ASIC IFC P1 STREAMS IFC - BIDIR BIDIR IFC P1 P2 P2 P3 Multiple Data Streams IN IFC OUT IFC Kernel OUT IFC IN IFC DATA I/O P1 STREAMS IFC OUT IN IFC P1 P2 P2 STREAMS IFC IN OUT IFC P3 I/O Interfaces COMM Interfaces C40 DSP Altera FPGA Real-Time Schedules, Communication Maps VHDL for FPGA Configs

3’ 3 B B 1 1’ 2 2’ c c d d e e Difficulties in ManagingGraphically Specified Constraints Change Maintenance??? Multiple Levels of Hierarchy A 4 Replicated Structures F B 4 1’’ 2’’ c d e Context Sensitive

Constraints Are Critical!! • Define functional properties of system • Ensure proper component interaction • Designer’s leverage to guide synthesis • Bad Constraint Management = Inflexible, unwieldy development.

Aspect-OrientedConstraint Language • Develop Language for Specifying Constraints • Operational • Mode-dependent behavior • Performance • Timing • Cost: Power/Parts $/Volume/Weight • Composibility: (Part A ~ Part B, Part C !~ Part D) • Resource: Process X requires Part D • Relationships to Modeling Aspects

Constraint ApplicationStrategy Language • Specify how to apply constraints across object hierarchy. • Determines how constraints are divided/responsibility shared among components. • Flexible to permit different goals • Latency optimization • Throughput optimization • ….

Demonstration Plans Waveform #1 Waveform #2 Unconstrained SW Radio Real-Time Design Weaver Strategy SW “RF” Components Synthesis Runtime Infrastructure