Advanced Standard-Cell Placer: Dragon by Northwestern Univ/UCLA for Efficient Layout Design

Dragon, developed by M. Sarrafzadeh's group at Northwestern University and UCLA, is a state-of-the-art standard-cell placer utilizing a hierarchical approach for integrated circuit design. It creatively combines advanced hypergraph-partitioning (hMetis) with bin-based simulated annealing techniques to minimize total bounding box wirelength and alleviate post-processing congestion issues. Dragon supports GSRC Bookshelf formats, supplying benchmarks in the same format, including the IBM-Dragon benchmark. For more information, visit: http://www.cs.ucla.edu/~xjyang/Dragon/.

Advanced Standard-Cell Placer: Dragon by Northwestern Univ/UCLA for Efficient Layout Design

E N D

Presentation Transcript

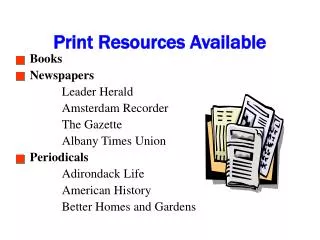

Bookshelf available resources Dragon • Dragon: A standard-cell placer (by Northwestern Univ/UCLA M. Sarrafzadeh’s group) • Hierarchical approach • Integrates state-of-the-art hypergraph-partitioning (hMetis) and bin-based simulated annealing • Total bounding box wirelength minimization • Post-processing congestion miminization • Support GSRC Bookshelf format • Benchmarks available in GSRC format • IBM-Dragon benchmark and Dragon’s outputs • http://www.cs.ucla.edu/~xjyang/Dragon/ 1