6-5 Microoperation

Understand microoperations like transfer, arithmetic, logic, bitwise AND/OR, and shift to manipulate data efficiently. Learn about shift registers for serial and parallel data handling. Design specialized counters.

6-5 Microoperation

E N D

Presentation Transcript

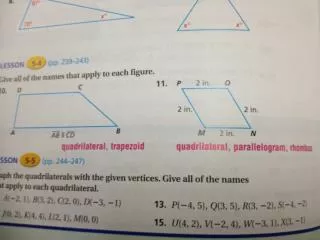

6-5 Microoperation • An elementary operations performed on data stored in registers or in memory. • Transfer • Arithmetic • Logic: perform bit manipulation on data in register • Bitwise AND, Bitwise OR …. • Shift

Arithmetic Microoperations • The control variable X selects the operation, and the control variable K1 loads the result in to R1. Fig. 6.6 Implementation

Logic Microoperations • manipulate the bits stored in a register • consider each bit in register separately

Logic Microoperations • Mask: allow us to deal with some specific bits • R1: 10101101 10101011 (data) • R2: 00000000 11111111 (mask) • 00000000 10101011 <=R1 ←R1^R2

Logic Microoperations • R1: 10101101 10101011 (data) • R2: 11111111 00000000 (mask) • 11111111 10101011 <=R1 ←R1˅R2 • R1: 10101101 10101011 (data) • R2: 11111111 00000000 (mask) • 01010010 10101011 <=R1 ←R1 R2

Shift Microoperations • shift left/shift right • incoming bit/outgoing bit

6-6 Microoperation on A single Register • Multiplexer-based transfer • if (K1=1) then (R0 ← R1) else if (K2=1) then (R0 ← R2) K1: R0← R1, R0 ← R2

Multiplexer-based transfer • Generalization of Multiplexer selection for n sources

Shift Registers • Serial input (SI) • Serial output (SO)

Bidirectional Shift Register One stage diagram

Ripple counter • Structure similar to ripple adder

Synchronous Binary Counter -Serial gating Fig. 3-52

Synchronous Binary Counter -Parallel gating Four AND gates delay Only one AND gate delay

Up-Down Binary Counter S=0 up counter S=1 down counter Homework #2 (deadline 12/??) Prove it and draw the logic diagram

Binary counter with parallel load It is a case of the up-down counter in the previous slide. (why? what case?) Fig. 6-14

BCD counter • A divide-by-N counter (modulo-N counter) is a counter goes through a repeated sequence of N states Fig. 6-15

Homework #3 (deadline 1/??/2017 ) • Design a counter with sequence 0,3,2,1,5,4,7 • Run the simulation for the designed circuit by using Quartus II • Deal with the unused state as don’t care • Test (manually) the circuit when the unused state occurs (manual or simulation)