Introduction

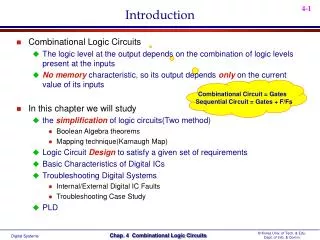

Introduction. Combinational Logic Circuits The logic level at the output depends on the combination of logic levels present at the inputs No memory characteristic, so its output depends only on the current value of its inputs In this chapter we will study

Introduction

E N D

Presentation Transcript

Introduction • Combinational Logic Circuits • The logic level at the output depends on the combination of logic levels present at the inputs • No memory characteristic, so its output depends only on the current value of its inputs • In this chapter we will study • the simplification of logic circuits(Two method) • Boolean Algebra theorems • Mapping technique(Karnaugh Map) • Logic Circuit Design to satisfy a given set of requirements • Basic Characteristics of Digital ICs • Troubleshooting Digital Systems • Internal/External Digital IC Faults • Troubleshooting Case Study • PLD Combinational Circuit = Gates Sequential Circuit = Gates + F/Fs

4-1 Sum-of-Products Form • Two or more AND terms that are ORed together • Each AND term consists of one or more variables individually appearing in either complemented or uncomplemented form • One inversion sign cannot cover more than one variable in a term • e.g., we cannot have ABC or RST • Product-of-Sums • Two or more OR terms that are ANDed together • Each OR term contains one or more variables in complemented or uncomplemented • The methods of circuit simplification and design based on the sum-of-Products form(주로 사용) • 4-2 Simplifying Logic Circuits • Fig. 4-1 : produce a more efficient implementation • Two methods for simplifying logic circuits • Boolean Algebra Theorems : greatly dependent on inspiration and experience • Karnaugh mapping : systematic and step-by-step approach Fig. 4-1

4-3 Algebraic Simplification • No easy way to tell whether the simplified expression is in its simplest form or whether it could have been simplified further • Algebraic simplification often becomes a process of trial and error • With experience, however, one can become adept at obtaining reasonably good results • Two essential steps to simplify the expression • Repeated application of DeMorgan’s theorems and multiplication of terms • Product terms are checked for common factors. Hopefully, the factoring results in the elimination of one or more terms 가능하면Sum-of-Product 형태로 만든 후 • Exam. 4-1 : Simplify the logic circuits shown in Fig. 4-2(a) • Exam. 4-2 : Simplify the expression Method 2 Method 1

Exam. 4-3 : Simplify the expression • 4-4 Designing Combinational Logic Circuits • Converting truth table to logic circuit • Forming AND term for each row with 1 in output • AND gate with appropriate inputs can be used to produce a 1 output for a specific set of input levels : Fig. 4-5 • AND gate outputs are ORed together to produce the total output x = • Exam. 4-4 : Simplify the expression • Exam. 4-5 : Simplify the circuit of Fig. 4-3(a) • Exam. 4-6 : Simplify the expression • You can try, but you will not be able to simplify this expression any further Simplification process produced an equivalent, but not simpler. Fig. 4-3(b) contain the same number of gates Fig. 4-4 Circuit that produces a 1 output only for the A=0, B=1 condition Fig. 4-6 AND outputs are ORed to produce final output

The same procedure can be extended to examples with more than two inputs : Tab. 4-1 • Complete Design Procedure 1) Convert truth table to sum-of-product 2) Simplify(Algebraic Simplification : Section 4-3) 3) Implement by using AND, OR, and Inverter gates • Exam. 4-7 : Design a logic circuit that has three input whose output will be HIGH only when a majority of the inputs are HIGH • Step 1. Setup the truth table • 1의 개수가 2개 이상일 때 : Tab. 4-2 • Step 2. Write the AND term for each case where the output is a 1 • Step 3. Write the sum-of-products expression for the output • Step 4. Simplify the output expression • Step 5. Implement the circuit for the final expression • Fig. 4-7 ABC 2개 추가

Exam. 4-8 : Design a logic circuit to produce a HIGH output as long as the binary value is greater than 6 Volt(refer to Fig. 4-8(a), orbiting spaceship) • From the truth table of Fig. 4-8(b) • Above expression is implemented in Fig. 4-8(c) • The algebraic simplification method can be quite lengthy when the original expression contains a large number of terms(따라서 이런 경우 K-Map 사용)

Exam. 4-9 : Design a logic circuit to produce a HIGH output signal S whenever either “no pager” or “jam”, and implement it using the 74LS00 chip(refer to Fig. 4-9(a), copy machine). • Truth table : Table 4-3 • No paper(P=0) or Jam(Q=R=1 and P=1) • AND/OR implementation : Fig. 4-9(b) • NAND implementation : Fig. 4-9(d) • Final wired-up of the circuit showing IC pin numbers, power pin, output driver transistor, and LED : Fig. 4-10 • 4-5 Karnaugh Map Method • A graphical device used to simplify a logic equation or convert truth table to logic equation • Limited to problems with 5 or 6 inputs(best for 4 or fewer inputs) • Karnaugh Map Format : Fig. 4-11 • Looping : • The process for combining those squares which contain 1s.

Looping Groups of Two(pairs) • Only the A variable appears in both uncomplemented and complemented form These two term can be looped the A variable eliminated since it appears in both uncomplemented and complemented forms : Fig. 4-12(a) • Looping a pair of adjacent 1s in a K map eliminates the variable that appears in complemented and uncomplemented form • Looping Groups of Four(Quads) • Both A and B appear in complemented and uncomplemented form(only variable C remains unchanged) : Fig. 4-13(a) • Looping a quad of 1s eliminates the two variables that appears in both complemented and uncomplemented form * 공통으로 묶으면 없어짐

Looping Groups of Eight(Octets) • Only variable B in in the same form for all eight squares, the other variables appear in complemented and uncomplemented form(only variable B remains unchanged) : Fig. 4-14(a) • Looping an octet of 1s eliminates the three variables that appears in both complemented and uncomplemented form • Complete Simplification Process • Summarize the rule for loops • When a variable appears in both complemented and uncomplemented form within a loop, that variable is eliminated from the expression. Variables that are the same for all squares of the loop must appear in the final expression • K-Map Method • Step 1 : Construct the K map and place 1s in those squares corresponding to the in the truth table. Place 0s in the other squares • Step 2 : Examine the map for adjacent 1s and loop those 1s which are not adjacent to any other 1s. These are called isolated 1s(1개) • Step 3(2개), Step 4(8개), Step 5(4개) • Step 6 : Loop any pairs necessary to include any 1s that have not yet been looped, making sure to use the minimum number of loops • Step 7 : Form the OR sum of all the terms * 2개로 우선 묶은 것은 나중에 8 또는 4개에 포함 가능 *그리고 크게 묶을 수록 더욱 간략화 *전체 묶음=1 : 위의 Fig. 4-14(a),(c)에서 X=B+B’=1

Exam. 4-10 ~ Exam. 4-12 : K-Map Examples Fig. 4-15(a), (b), (c) • Exam. 4-13: The same K map with 2 equally good solutions Fig. 4-16(a), (b) • Filling K Map from Output Expression • 1. Get the expression into SOP form if it is not already so. • 2. For each product term in the SOP expression • Place a 1 in each K-map square whose label contains the same combination of input variables. • Place a 0 in all other squares. • Exam. 4-14 illustrates this procedure • Exam. 4-14: Use the K map to simplify the expression • Fig. 4-17 • “Don’t -Care” Conditions • “Don’t-Care” whether the output is HIGH or LOW : Fig. 4-18(a), (b) • “Don’t-Care” conditions should be changed to 0 or 1 to produce K-map looping that yields the simplest expression : Fig. 4-18(c) • Exam. 4-15 illustrates this procedure

Exam. 4-15: Design an elevator door controller in a 3-story building - Fig. 4-19 • 4 input variables : • M (Moving Sensor) : 1(Moving) / 0(Stopped) • F1, F2, F3 (Floor indicator Sensor) : 0(Normally) / 1(positioned at any particular floor) • 1 output variable : • Door Open Signal : 0(normally) / 1(door open) • M=1 일때 모두 0=Close • 4-6 Exclusive-OR/NOR Circuits • Exclusive-OR • Output x=1 for two cases: A=0, B=1 and A=1, B=0 • This circuit produces a HIGH output whenever the two inputs are at opposite levels(Fig. 4-20 : symbol, truth table) • Available EX-OR gate IC : 74LS86, 74C86, 74HC86 • Exclusive-NOR • Output x=1 for two cases: A=B=1 and A=B=0 • This circuit produces a HIGH output whenever the two inputs are at the same levels(Fig. 4-21 : symbol, truth table) • Available EX-OR gate IC : 74LS266, 74C266, 74HC266

Exam. 4-16: Determine the output waveform for the input in Fig. 4-22 • Exam. 4-17: Design a logic circuit to produce HIGH only when the two binary numbers y1y0 and x1 x0 are equal • Truth Table : Tab. 4-4, Logic Circuit : Fig. 4-23 • Exam. 4-18: Simplify the circuit of Fig. 4-24(a) • Simplified Logic Circuit : Fig. 4-24(b) • 4-7 Parity Generator and Checker • Even Parity Generator : Fig. 4-25(a) • 4 data + 1 parity bit • the total number of 1s (including the parity bit) is aneven number • Even Parity Checker : Fig. 4-25(b) • Five bits(data+parity) enter the receiver’s parity checker circuit, and produce an error output E(E=0 : No error, E=1 : Error) • Same as 5 bit parity generator • Exam. 4-19: Determine parity generator’s output • Exam. 4-20: Determine parity checker’s output y1 = x1 and x0 = y0 y1y0 = x1 x0 XNOR 사용 No error P D3 D2 D1 D0 E 1 1 0 1 1 0

참고 사항 C A C B A B D • Map • 2 variables • 3 variables • 4 variables B A • 5 variables C B A D E F

참고 사항 • Adjacent Square • Number of square = 2n (1, 2, 4, 8, ….) • The squares at the extreme ends of the same horizontal row are to be considered adjacent • The same applies to the top and bottom squares of a column • The four corner squares of a map must be considered to be adjacent • Groups of combined adjacent squares may share one or more squares with one or more group

참고 사항 C B A D • Odd Parity Generator/Checker • Truth Table • K-Map(Odd Parity) • Expression

Control Input B • 4-8 Enable/Disable Circuits • The basic logic gates can be used for control : Fig. 4-26 • A logic signal “A” is applied to one input of each of the basic logic gates, and The other input of each gate is the control input “B” • Control input “B” can either enable or disable the passage of an input signal “A” • This controlling action is why these circuits came to be called gates • When the non-inverting gates(AND, OR) are enabled, the output will follow the A signal exactly. • Conversely, when the inverting gates(NAND, NOR) are enabled, the output will be the exact inverse of the A signal • Exam. 4-21: Design a logic circuit that will allow a signal to pass to the output only when control inputs B and C are both HIGH; otherwise, the output will stay LOW- Fig. 4-27(a) • Exam. 4-22: Design a logic circuit that allows a signal to pass to the output only when one, but not both, of the control inputs are HIGH; otherwise, the output will stay HIGH - Fig. 4-27(b) • Exam. 4-23: 1) B=1, output x will follow input A, and output Y will be 0 - Fig. 4-28 2) B=0, output x will be 0, and output Y will follow input A Signal Input A

4-9 Basic Characteristics of Digital ICs • Digital IC • A collection of resistors, diodes, and transistors fabricated on a single piece of semiconductor material(Substrate or Chip) • Package Type : refer to p. 422 • The chip is enclosed in a protective plastic or ceramic package • Fig. 4-29 (a) DIP, (b) top view, (c) actual silicon chip • Classified by circuit complexity • The number of logic gates on the chip : Tab. 4-5 • Bipolar/Unipolar Digital ICs : refer to p. 425, 446 • Bipolar IC : bipolar junction transistors(NPN and PNP) are used • TTL family IC : Fig. 4-30(a) TTL inverter • Unipolar IC : unipolar field-effect transistors(P and N-channel) are used • CMOS family IC : Fig. 4-30(b) CMOS inverter

Package Types • Small Outline Transistor (SOT) • Small Outline Package (SOP) • Dual-In-Line Package (DIP) • Plastic/Ceramic Pin Grid Array (PPGA/CPGA) • Plastic Leaded Chip Carrier (PLCC)

Ceramic Leadless Chip Carrier (LCC) • Plastic Quad Flat Package (PQFP) • TO Packages (Transistor single Outline)

i Pt Si V 0.2 0.4 0.6 Forward Bias Schottky Diode 54 Series : -55 ° C 125 °C, Military 74 Series : 0 ° C 70 ° C, Commercial • TTL Family • Various series within the TTL logic family : Tab. 4-6 • The differences between the various TTL series • Electrical characteristics : such as power dissipation, delay times, switching speed • No difference in the pin layout or logic operations • CMOS Family • Several CMOS series are listed : Tab. 4-7 • Power and Ground • The most important connections are dc power and ground • VCC(collector) for TTL circuit, VDD(Drain) for CMOS circuit *Schottky Diode : p. 433 금속과 반도체를 연결하면 ECL 보다는 느리지만 동작속도가 빨라짐( 0.4 Volt에서 동작) 4000 Series(RCA), MC14500(Motorola), 5000(Toshiba)

Logic-Level Voltage Ranges : Fig. 4-31 • TTL: VCC is nominally +5V • Logic 0 from 0 V to 0.8 V • Logic 1 from 2 V to 5 V • CMOS: VDD can range between +3V to +18V • Logic 0 from 0 V to 1.5 V • Logic 1 from 3.5 V to 5 V • Indeterminate Range : TTL(0.8 2.0 V), CMOS(1.5 3.5 V) • The IC manufacturer can not guarantee how a TTL/CMOS circuit will respond to indeterminate input levels • Unconnected(Floating) Inputs • TTL : Floating input acts like logic 1(not recommended in practice) • A DC level of floating TTL input = 1.4 1.8 V • CMOS : Floating input may damage chip(overheated) • all unused inputs must be connected to a LOW or a HIGH level • Voltage level fluctuates with noise(not a specific DC voltage level) • Unpredictable output(output will oscillate as a result of the noise picked up by the floating input) • Logic Circuit Connection Diagrams : Fig. 4-32 • All electrical connection, pin number, IC number, component value, signal name, power supply voltage

4-10 Troubleshooting Digital Systems • Three basic steps in fixing a digital circuit or system • 1) Fault Detection • 2) Fault Isolation • 3) Fault Correction • The actual troubleshooting procedure highly depend on the type and complexity of the circuitry, and on the kinds of troubleshooting tools and documentation that are available • Good troubleshooting techniques can be learned only in a laboratory environment through experimentation and actual troubleshooting of faulty circuits and systems • There is absolutely no better way to become an effective troubleshooter than to do as much troubleshooting as possible, and no amount of textbook reading can provide that kind of experience • The basic troubleshooting tools available : logic probe, oscilloscope, logic pulser, current tracer • The most important and effective troubleshooting tool is the technician’s brain • In the next three sections on troubleshooting, we will use only our brain and a logic probe - Fig. 4-33

4-11 Internal Digital IC faults • The most common internal failures of digital ICs • 1) Malfunction in the internal circuitry • 2) Inputs or outputs shorted to ground or Vcc • 3) Inputs or outputs open-circuited • 4) Short between two pins • Malfunction in the internal circuitry • The IC outputs do not respond properly to the IC inputs(internal component has failed : Fig. 4-30(a) Base-emitter short in Q4) • This type of failure is not as common as the other three • Input/output Internally Shorted to Ground or Supply • Input shorted to ground and supply voltage : Fig. 4-34(a), (b) • Output shorted to ground and supply voltage : Fig. 4-34(c), (d) • Exam. 4-24: Suggest some of the possible faults -Fig. 4-35 • 1) Malfunction in the internal circuitry(INVERTER) • 2) Output pin 4 of the INVERTER could be shorted to ground internally • 3) Input pin 1 of NAND could be shorted to ground internally

Open-Circuited Input or Output • the very fine conducting wire will break, producing an open circuit(Floating State) : Fig. 4-36 • Exam. 4-25: What would a logic probe indicate at pin 13 and at pin 6 of Fig. 4-36? • Pin 13 : the external signal level that connected to pin 13(not shown in this diagram) • Pin6 : Indeterminate logic level(Floating) • Exam. 4-26: What are possible fault that could produce the recorded results? Assume that the ICs are TTL? • Non-faulty NAND output should be HIGH(p. 141) • LOW at Input pin 1 of NAND gate is not reaching the internal NAND gate circuitry because of an internal open • TTL : Open input = High input • CMOS : Open input = indeterminate output, and overheating * Fault 상태에서 NAND gate의 출력이 pulsing 한다는 의미는 NAND gate의 Pin 1에 1(HIGH)이 입력되고 있음 1 0 0 1 1

Short Between Two Pins • Pins 5 and 6 of the NOR gate are internally shorted : Fig. 4-38 • t1 to t2 : both INVERTER has HIGH input(inverted to both LOW) • t2 to t4 : one INVERTER is HIGH while the other is LOW(Indeterminate range) • t4 to t5 : both INVERTER has LOW input(inverted to both HIGH) • 4-12 External Faults • Open Signal Lines • Broken wire, Poor solder connection, crack or cut trace on PCB, Bent or Broken pin on an IC, Fault IC socket(bad contact with IC pin) • This type of circuit fault can often be detected by • a careful visual inspection • checking continuity with an ohmmeter(Power off 상태에서) • Exam. 4-27: What is the most possible circuit fault(CMOS circuit of Fig. 4-39)? • Open circuit in the signal path between pin 6 of Z1 and pin 2 of Z2 • Trace the signal path between pin 6 of Z1 and pin 2 of Z2 PCB상의 Pattern(신호선)

Shorted Signal Line • This type of fault has the same effect as an internal short between IC pins • Sloppy wiring : 전선 피복을 너무 많이 벗겨서 벗겨진 부분이 근처에 shorted • Solder bridges : 아주 인접한 두 pin사이에 생김 • Incomplete etching : PCB상에 구리가 부식되어 없어지지 않고 그대로 남이 있음 • Faulty Power Supply • Power 자체의 고장 또는 Overloaded(drawing more current than the supply is designed for) • Good troubleshooting practice is to check the voltage levels at each power supply(또한 oscilloscope를 사용하여 ac ripple 또는 rectified 되는지 확인) • One of the most common signs of a faulty power supply is one or more chips operating erratically or not at all(because some ICs are more tolerant of power supply variations and may operate properly, while others do not) • Always check the power and ground levels at each IC. • Output Loading : Fan-in / Fan-out(p. 435) • 4-13 Troubleshooting Case Study • Exam. 4-28: Develop a step-by-step procedure to determine the exact fault(Input A=B=0, C=1 and Fig. 4-40) • Non fault : The EX-OR gate should be producing a LOW at output pin3, since both of its inputs are at the same LOW level

Current fault : Z1-3 is stuck HIGH • Possible faults • 1) Internal component failure in Z1 • 2) Node X와 연결된 모든 선에 대한 external short to Vcc • 3) Pin 3 of Z1 internally shorted to Vcc • 4) Pin 5 of Z2 internally shorted to Vcc • 5) Pin 13 of Z2 internally shorted to Vcc • Procedure to isolate the fault • 1) Z1의 전원 확인(Vcc 와 ground) • 2) Power-off후, Ohm meter를 사용하여 node X와 Vcc(pint 14 of Z1 and Z2)사이의 short 확인(만약 no short이면 Z1 internal fault, 따라서 Z1 교체) • 3) 만약 step 2)에서 short 이면 node X가 Vcc에 short된 지점을 Visual 검사(solder bridges, unetched copper, uninsulated wires,….)를 통해 찾는다(만약 short된 지점을 찾았으면 이를 제거하고 Ohm meter를 사용하여 node X 가 더 이상 Vcc에 short 되지 않는지를 확인) • 4) 만약 step 3)에서도 고장이 발견되지 않으면 Z1-3, Z2-13, 또는 Z2-5 중에 하나가 Vcc에 Internally shorted. • 5) Z1-3, Z2-13, 또는 Z2-5 를 각각 한 개 씩 절단한 후 node X가 그래도 Vcc에 short되었는지 확인, 만약에 세개중에서 어느 한 개를 절단한 후 node X가 더 이상 short되지 않으면 완료 되었음 • ICs are in socket : socket에서 뽑은 후, suspected pin을 구부리고 다시 삽입 • ICs are soldered : have to cut the trace, 그리고 나중에 repair

4-14 Programmable Logic Devices • Common approach to implementing logic functions • The last step in the design of a logic circuit is to gather the appropriate ICs and make the proper connections so that the circuit’s outputs are the desired logic functions of the circuit’s input • Especially useful in implementing more complex circuits containing tens or hundreds of logic gates = PLD(Programmable Logic Device) • Simplified example of a PLD : Fig. 4-41

The sum-of-products structure with AND gates feeding a final OR gate 1) AND : Link 1, 2, 3 = Open, Link 4 = Connect 2) XOR : Link 1, 4 = Open, Link 2, 3 = Connect • Programming = Fuse blowing(Links) • Study in detail Chap. 12 • A PLD development system : Fig. 4-42 • Combinational circuit design example : Exam. 4-7, p. 117 • PLD development cycle flowchart : Fig. 4-46 • Test vectors : • A set of hypothetical inputs and corresponding outputs will prove that the device works as expected Tab. 4-8 • Generating a JEDEC(Joint Electronic Device • Eng. Council) file to programmer. • PALASM : Low-level PAL Assembler • HDL : More powerful logic Compiler • 1) ABEL : Data I/O Corp. • 2) CUPL : Logical Device, Inc • -CUPL input file : Fig. 4-44 • -Wired circuit : Fig. 4-45 * 3 methods of circuit design input: Fig. 4-43