Embedded System Bus Communication Process and Timing

DESCRIPTION

Explore the intricate workings of an embedded system bus with detailed discussions on addressing, data transfer, interrupts, and memory operations. Learn about the clock cycles and protocol involved in high-speed communication.

1 / 6

Télécharger la présentation

Embedded System Bus Communication Process and Timing

An Image/Link below is provided (as is) to download presentation

Download Policy: Content on the Website is provided to you AS IS for your information and personal use and may not be sold / licensed / shared on other websites without getting consent from its author.

Content is provided to you AS IS for your information and personal use only.

Download presentation by click this link.

While downloading, if for some reason you are not able to download a presentation, the publisher may have deleted the file from their server.

During download, if you can't get a presentation, the file might be deleted by the publisher.

E N D

Presentation Transcript

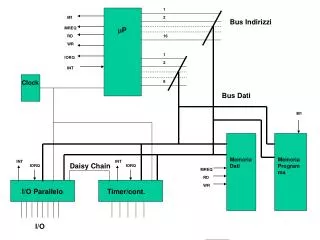

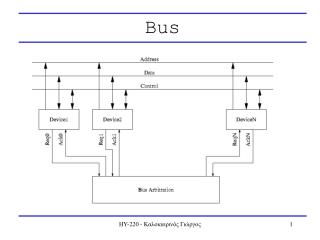

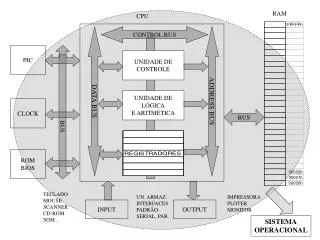

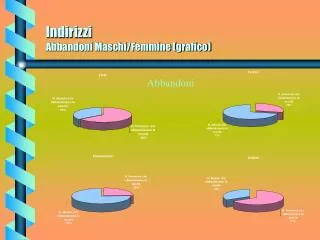

1 M1 2 Bus Indirizzi MREQ P RD 16 WR 1 IORQ 2 INT Clock 8 Bus Dati M1 Memoria Dati Memoria Programma INT INT Daisy Chain IORQ IORQ MREQ RD WR I/O Parallelo Timer/cont. I/O

T1 T2 T3 T4 T5 Clock M1 Addr MREQ RD Data Ciclo OP CODE Fetch

T1 T2 T3 T4 T5 Clock Addr MREQ WR Data Ciclo Memory Write

T1 T2 T3 T4 T5 Clock Addr IORQ WR Data Ciclo I/O Write

T1 T2 T3 T4 T5 Clock INT M1 Addr IORQ RD Data Ciclo Interrupt

More Related