Input Output

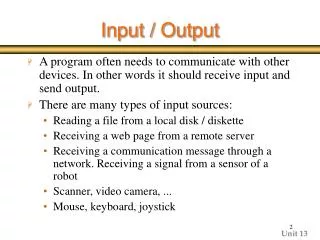

Chapter 4. Input Output. CS.216 Computer Architecture and Organization. Overview (1/2). Input / Output modules are the third critical element of the computer system (others are the CPU and the memory) All computer systems must have efficient means to receive input and deliver output

Input Output

E N D

Presentation Transcript

Chapter 4 Input Output CS.216 Computer Architecture and Organization

Overview(1/2) • Input / Output modules are the third critical element of the computer system (others are the CPU and the memory) • All computer systems must have efficient means to receive input and deliver output • Failure to address I/O concerns has doomed many otherwise good systems

Overview(2/2) • We will look at • I/O modules and their interface to the rest of the system • I/O mechanisms • Example interfaces • Reading: Text, Chapter 6

I/O Modules(1/5) • External devices are not generally connected directly into the bus structure of the computer • Wide variety of devices require different logic interfaces -- impractical to expect CPU to “know how” to control each device • Mismatch of data rates • Different data representations

I/O Modules(2/5) • The I/O module • Provides a standard interface to the CPU and the bus • Tailored to specific I/O device and its interface requirements • Relieves the CPU of the management of the I/O devices • Interface consists of • Control • Status and • Data signals

Programmed I/O(1/3) • I/O operation in which CPU issues the I/O command to the I/O module • CPU is in direct control of the operation • CPU waits until the I/O operation is completed before it can perform other tasks • Completion indicated by a change in the module status bits • CPU must periodically poll the module to check its status

Programmed I/O(2/3) • As a result of the speed difference between a CPU and the peripheral devices (orders of magnitude), programmed I/O wastes an enormous amount of CPU processing power • Very inefficient • CPU slowed to the speed of the peripheral • Advantages • Simple to implement • Requires very little special software or hardware

Figure 7.5aThree Techniques for Input of a Block of Data

I/O addressing(1/3) • Isolated (standard) I/O • Address space of the I/O modules is isolated from the memory address space • Separate instructions in the instruction set are used to perform I/O • Typical control lines include the read/write lines plus an IO/M line to switch address reference between memory space and I/O space

I/O addressing(2/3) • Memory mapped I/O • I/O devices are integrated into the normal memory address space • All of the memory accessing instructions can be used to access the I/O peripherals • “Cost” is the loss of “real” memory addresses • Not a big problem today with the huge address spaces in current systems

Interrupt-Driven I/O(1/11) • To reduce the time spent on I/O operations, the CPU can use an interrupt-driven approach • CPU issues I/O command to the module • CPU continues with its other tasks while the module performs its task • Module signals the CPU when the I/O operation is finished (the interrupt) • CPU responds to the interrupt by executing an interrupt service routine and then continues on with its primary task

Interrupt-Driven I/O(2/11) • CPU recognizes and responds to interrupts at the end of an instruction execution cycle • Interrupt technique is used to support a wide variety of devices

Interrupt-Driven I/O(3/11) Figure 7.5b Three Techniques for Input of a Block of Data

Figure 7.8aChanges in Memory and Registers for an Interrupt

Figure 7.8bChanges in Memory and Registers for an Interrupt

Interrupt-Driven I/O(7/11) • Design issues -- with multiple modules and thus multiple interrupts • How does the CPU determine which device caused the interrupt? • If multiple interrupts occur at the same time, which is processed first?

Interrupt-Driven I/O(8/11) • Interrupt determination • Provide multiple interrupt signal lines for a system • Practical only for small numbers of interrupts • Use 1 interrupt for more than 1 device • Must perform some sort of device polling to determine which requested service • Requesting device can place an ID on the bus -- vectored interrupts • Bus arbitration and vectored interrupts

Daisy Chain ‘1’ 1 2 EI EI EI EI EO EO EO EO 3 4 Interrupt-Driven I/O(9/11) • Determination scheme prioritizes multiple interrupts • Centralize Interrupt Control • Intel 8259 • Distributed Interrupt Control • Daisy Chain ‘0’ ‘1’ ‘1’ ‘0’ Int ‘0’ ‘0’ ‘1’ ‘0’

Direct Memory Access(1/9) • Both programmed and interrupt driven I/O require the continued involvement of the CPU in ongoing I/O operations • Direct memory accessing takes the CPU out of the task except for initialization of the operation

Direct Memory Access(2/9) • Large amounts of data can be transferred between memory and the peripheral w/o severely impacting CPU performance • CPU initializes DMA module • Read or write operation defined • I/O device involved • Starting address of memory block • Number of words to be transferred • CPU then continues with other work

Direct Memory Access(3/9) Figure 7.5cThree Techniques for Input of a Block of Data

Direct Memory Access(6/9) • DMA operates by “stealing” bus cycles from the CPU • In theory, it uses the bus when the CPU is not using it -- no impact on the CPU performance • In practice, it steals cycle when CPU is go to use bus. • Accesses memory to retrieve a data word • Forwards the word to the I/O peripheral

External Interface(1/9) • The external interface, made with the I/O module, must be tailored to the nature and operation of the peripheral • Parallel vs. serial data transfers • Data format conversions • Transfer rates • Number of devices supported

External Interface(2/9) • Examples • RS-232 serial ports • Game ports • High speed I/O buses • Support external mass storage devices and multimedia devices

External Interface(5/9) • Small Computer System Interface (SCSI) • Introduced by Apple in 1984 • Used to interface a wide variety of high speed devices to the computer system • While called a “bus” it is really a mechanism to daisy chain devices together

External Interface(6/9) • SCSI-1 • Used 8-bit data bus width • 5 MHz clock -- transfer rate of 5 MB/sec • Supported up to 7 devices (compare to the 2 of a typical IDE configuration) • SCSI-2 • Current standard • Expands the bus width to 16 or 32 bits • Clock rate of 10 MHz • Supports wide variety of device types, making I/O software in the host simplier

External Interface(8/9) • P1394 High Performance Serial Bus • High speed, low cost serial link • Gaining support in consumer electronics products as well as computer systems • Deliberately move away from parallel connections with associated high cable and connector costs

External Interface(9/9) • Provide high speed serial link (25-400 Mbps) that is able to connect to many devices • Daisy chain up to 63 devices together on 1 bus, interconnect up to 1022 buses together through bridging techniques • Communication is based on a 3-layer protocol • Physical layer • Link layer • Transaction layer

Do you have any Question!