Precision Control of ADC Timing and Read Operations at 40 MHz

This document details the timing requirements for interfacing with a 40 MHz Analog-to-Digital Converter (ADC). It covers signal triggers, sampling window controls, and pulse widths essential for proper A/D conversion and data reading. Key aspects include the timing for triggering ADC conversion and clearing registers, as well as the necessary parameters for reading tokens from memory. Special focus is given to the precise timings of pulse widths, ensuring effective communication and data integrity in high-frequency environments.

Precision Control of ADC Timing and Read Operations at 40 MHz

E N D

Presentation Transcript

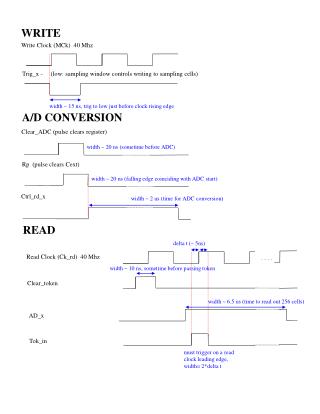

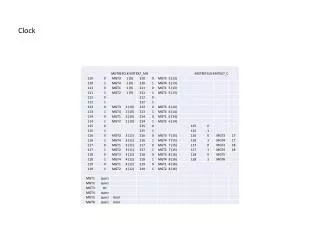

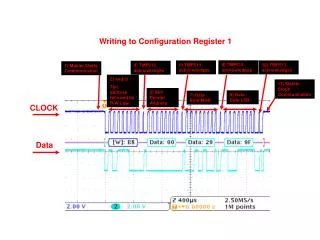

WRITE Write Clock (MCk) 40 Mhz Trig_x - (low: sampling window controls writing to sampling cells) width ~ 15 ns, trig to low just before clock rising edge A/D CONVERSION Clear_ADC (pulse clears register) width ~ 20 ns (sometime before ADC) Rp (pulse clears Cext) width ~ 20 ns (falling edge coinciding with ADC start) Ctrl_rd_x width ~ 2 us (time for ADC conversion) READ delta t (~ 5ns) Read Clock (Ck_rd) 40 Mhz . . . . width ~ 10 ns, sometime before passing token Clear_token width ~ 6.5 us (time to read out 256 cells) AD_x Tok_in must trigger on a read clock leading edge, width= 2*delta t

READ Read Clock (Ck_rd) 40 Mhz