ECE 320 Homework #3: Boolean Function Simplification and BCD Decoder Design

This homework assignment focuses on simplifying Boolean functions using don't care conditions in both Sum of Products (SOP) and Product of Sums (POS) forms. It includes multiple Boolean function examples to simplify, with relevant combinations of inputs. Additionally, students are required to analyze a two-output circuit from a given figure, deriving the logical expressions for each gate's output. An essential task also involves designing a minimum-gate-count combinational checking circuit for validating a 4-bit BCD number. Lastly, a BCD-to-seven-segment decoder needs to be designed based on a specified numeric designation.

ECE 320 Homework #3: Boolean Function Simplification and BCD Decoder Design

E N D

Presentation Transcript

ECE 320 Homework #3 • Simplify the Boolean function F using the don’t care conditions d, in both S.O.P. and P.O.S. form: • F=A’B’D’+A’CD+A’BC d=A’BC’D+ACD+AB’D’ • F=W’(X’Y+X’Y’+XYZ)+X’Z’(Y+W) d=W’X(Y’Z+YZ’)+WYZ • F=ACE+A’CD’E’+A’C’DE d=DE’+A’D’E+AD’E’ • F=B’DE’+A’BE+B’C’E’+A’BC’D’ d=BDE’+CD’E’

ECE 320 Homework #3 • Analyze the two output circuit shown in Figure below. Indicate the logical expression associated with every gate output. C F A B Z

ECE 320 Homework #3 • A 4-bit BCD number in 84-2-1 code is to be checked to determine whether the 4-bits represent the valid BCD number. Develop a minimum-gate-count combinational checking circuit whose output will be a 1 if the input is not a valid BCD number otherwise it will be a zero. • A BCD-to-seven-segment decoder is a combinational circuit that accepts a decimal digit in BCD and generates the appropriate outputs for selection of segments in a display indicator used for displaying the decimal digit. The seven outputs of the decoder (a,b,c,d,e,f,g) select the corresponding segments in the display as

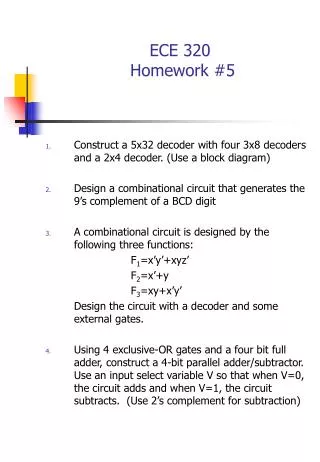

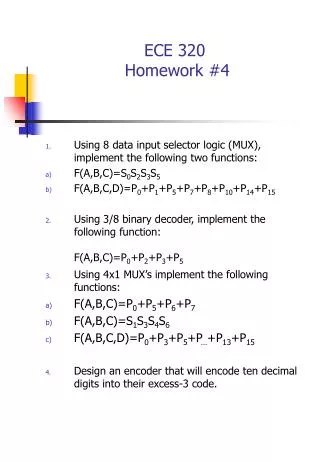

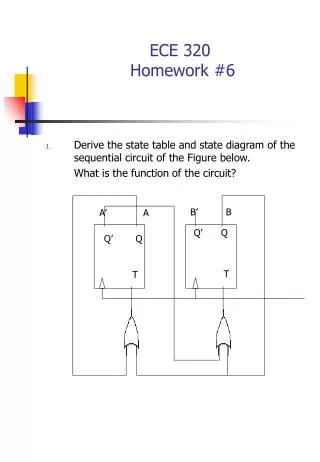

ECE 320 Homework #3 5. shown in Figure (a). The numeric designation chosen to represent the decimal digit is shown in Figure (b). Design the BCD-to-seven-segment decoder circuit. (a) Segment Designation (b) Numeric Designation