Dynamic NoC

E N D

Presentation Transcript

Limitations of Fixed NoC Communication • NoC for reconfigurable devices: • NOC: a viable infrastructure for communication among task dynamically placed on a reconfigurable device. • Too inflexible for a changing network: • When new task is scheduled: • If can fit in a PE, no problems: • place the component on one PE, • attach to its router. • Else, component is split into several PEs • PEs use router network for communication (packets) • resources are wasted, • slow.

DyNoC • DyNoC: • NoC whose structure can be dynamically changed at run-time. • Routers: • programmable elements basically configured as router • but can be configured at run-time to implement any function.

DyNoC • When a multiple-PE module is placed: • the redundant routers can be used as additional resources for the module. • The placed module only needs one router. • Routers in that area are no more accessible by other components. • Upon completion, • the module is removed and the network must be reactivated in that area. • Can be done quickly (because the router are programmable components that can be quickly reset to their basic configuration, i.e. the routers).

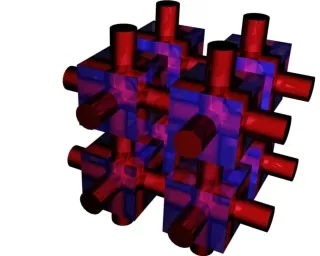

Communication Infrastructure • Goal: • Reachability of packets is insured, independent of the changing topology. • DyNoC Architecture: • A normal NoC. • Direct communication lines between neighboring PEs. • Split components do not need the router. • Direct lines can also be modified to connect two non-adjacent PEs.

Communication Infrastructure • Device is surrounded by a ring of routers. • Increases the flexibility • and a prerequisite for a accessibility of placed components. • Activation line: • Component notifies neighboring routers about their activity: • 1: no component is placed on top of that router. • 0: a component is using that router.

Network Access • Reminder: • Synthesis of components is done at compiled time. • Result of synthesis of a component: • A box that encapsulates the circuit which uses the resources in a given area (routers’ logic and PEs). • When a new component is placed at run-time, its coordinate is set to that of its corresponding router (e.g. NE). • Destroys some part of the network. • Goal: reachability: • Must insure that packets sent to other components will still reach their destination.

Reachability • Definition: Reachability of a component (pin): • Given a reconfigurable device and a configuration, a component (pin) on reconfigurable device at a given time is reachable if every message sent to this component (pin) can reach the component (pin). • Necessity: • At run time, the configuration of the chip is not known in advance, • we must insure that all components and pins on the device are reachable at any time during the temporal placement. • Necessary condition: • if at any time the set of components and pins on the device isstrongly connected.

Reachability • Definition: strongly connected configuration: • Given a reconfigurable device, a configuration of the device is strongly connected if for each pair of components A and B, a path of active routers that connects the two components, exists on the device.

Reachability • Two methods: • Placer takes care: • Highly complex placer • Synthesizer ensures it. • Theorem: • If each component is synthesized in such a way that it is internally surrounded only by PEs, then all placements on the reconfigurable device are strongly connected.

Reachability • Proof: • Assume that a set of components developed as required in the theorem and placed on the device PE is not strongly connected, then • at least two components abut • or one component abuts the device boundary. • Case1: • Either the two components overlap • Placer doesn’t allow this. • Or one component uses some routers on its boundary. • Contradiction.

Packet Routing • Problems: • Some routers are inactive • Not all routers have 4 neighbors • Common NoC routing algorithms cannot work. • Dynamic placement and removal of modules unpredictable obstacles in a DyNoC, • Adaptive routing algorithms • Algorithm must be: • fully local-decisive: • Decision where to send a packet is taken locally. • deadlock free, • livelock free.

S-XY-Routing(Surrounding XY-routing) • S-XY-Routing: 3 modes: • N-XY (Normal XY) mode: • The router behaves as a normal XY router. • SH-XY (Surround horizontal XY) mode: • The router enter this mode when its left (right) neighbor is deactivated. • SV-XY (surround vertical XY) mode: • The router enter this mode when its upper (lower) neighbor is deactivated.

S-XY-Routing • SH-XY (Surround horizontal XY) mode: • XY-routing: • If Ydest >= Yrouter: Choose path1 • Send the packet upward. • Else choose path2: • downward. • Problem: • Ping-pong

S-XY-Routing • Solution: • Setting a “stamp bit” for the packet: • Notifies the next routers that the packet is willing to surround the component, and it should not be sent back. • Upon reaching the router upper right of the obstacle: • stamp is removed, • the packet is sent left, until its destination column or until another obstacle.

S-XY-Routing • Guarantee: • Packet will never be blocked • because each component is always surrounded by a ring of routers. • Theorem: • With very high probability, the S-XY algorithm is deadlock free and livelock free. • Simple proof: in the text book.

S-XY-Routing • Problem: • Fixed direction on obstacles (e.g. right) • Long paths (in worst case) • Solution: • Guide the router around a component where to send the packets, when a packet is blocked.

Router Guiding • Router guiding: • Use an additional line: • 0: a packet blocked in the vertical (horizontal) direction must be forwarded east (north) • 1: a packet blocked in the vertical (horizontal) direction must be forwarded west (south) • The best direction is determined at compile-time by the component shape.

Analysis of Efficiency • Communication latency of a packet: • The number of routers on a path from its source to its destination. • On a reconfigurable device (worst case): W + H • On a DyNoC (with changing placement): Unpredictable: • Worst case delay of packet p: Dwc(p) = H +W +i=0,…kDiwc(p) • k: # of obstacles • Diwc(p): worst case additional delay caused by the obstacle i: • = max(wi, hi) • depends on the temporal placement. H W

Analysis of Efficiency • Pipelined communication: • Static NoC • Once the pipeline if filled, one packet is received at the destination on each clock. • DyNoC: • Delays created by newly placed components create new situations. • Even possible that some packets sent later arrive earlier.

Implementation • Area occupation / Memory usage / Frequency (MHz)

Implementation • Large routers • Can be much smaller if implemented special to the router.

References • [Bobda07] Christophe Bobda, “Introduction to Reconfigurable Computing: Architectures, Algorithms and Applications,” Springer, 2007. • [Bobda05] C. Bobda and A. Ahmadinia, “Dynamic interconnection of reconfigurable modules on reconfigurable devices.” IEEE Design & Test of Computers, vol. 22, no. 5, pp. 443–451, 2005.