Red Hat Linux Transition for MPC Testing Progress

Explore the transition to Linux environment for MPC testing procedures and solve software errors with flexible coding methods. Compare SBS API, AddHAL, and ItemHAL for VME access efficiency. Utilize console applications for efficient testing and monitoring of MPC functions.

Red Hat Linux Transition for MPC Testing Progress

E N D

Presentation Transcript

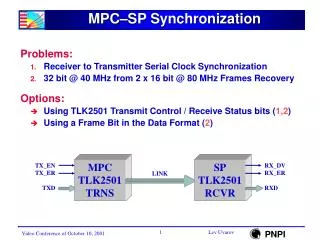

Transition to Linux Environment SBS Bit 3 Model 618 Red Hat Linux 7.0 2.2.16-22 1003 Software Errors Error: Install looks for Wrong Directory Solution: Make link to Real Directory Error: Loading Driver Solution: Need to power on Crate with VME Bus Controller Error: Byte Swapping of Word data Solution: Run program with Function bt_set_info()

Developed code for SBS API and HAL • Designed testing code to be flexible enough to use either VME classes that are HAL dependent or SBS API dependent • Three sets of VME classes:

Comparison of SBS API and HAL • SBS API Pros: Fastest VME Access Time Cons: Device/OS Dependent Need to have all VME address information in the code Exception Information Thrown is not as detailed as HAL’s Performance: On 200MHz machine takes ~20μs for one 16-bit read or write

Comparison of SBS API and HAL • AddHAL Pros: VME Device Independent VME address information stored in XML file, but need variables in code to take this information during runtime More Detailed Error Information Cons: Slower VME Access Time Performance: On 200MHz machine takes ~40μs for one 16-bit read or write

Comparison of SBS API and HAL • ItemHAL Pros: Most readable code Most Flexible: VME/PCI Device Independent VME address information stored in XML file. In code, only need item names Most Detailed Error Information Cons: Slowest VME Access Time Performance: On 200MHz machine takes ~65μs for one 16-bit unmaskedRead or unmaskedWrite

Comparison of SBS API and HAL For more information go to: http://hbar.rice.edu/~pawloski/HALvsAPI/APIvsHAL.html

MPC Testing Software • Created 3 primary C++ classes to control the MPC, TMB, and CCB. The TMB and CCB classes only have the needed functionality for testing the MPC. • For each class there are three sets of code for SBS, AddHAL, and ItemHAL VME access. • There is one set of Testing Software that can be compiled with any of the three class sets. • The Testing Software can compiled on either Linux or Windows. On Windows, only the SBS set of classes can be used. • There are four menu driven console applications in the Testing Software set.

Console 1: JTAG over VME • On the MPC at CSR0 there are 4 bits that are used to emulate the JTAG pins: TDI, TMS, TCK, and TDO • The JTAG Menu console can send such a JTAG signal and convert BIT, MCS, and SVF files into a VME bit stream that can be read by the program.

Console 1: JTAG over VME • In the JTAG Menu there are 8 options: 1. Convert a SVF file into VME bit stream files with the extensions ‘.vme’ and ‘.cvme’ 2. Convert a MCS file into VME bit stream files that will program the MPC XC18V04 EPROM. 3. Use a ‘.vme’ or ‘.cvme’ file to send a JTAG signal over VME 4. Verify Configuration in MPC PROM with SVF file 5. Verify Configuration in MPC PROM with MCS file 6. Erase MPC PROM 7. Hard Reset of MPC FPGA (not JTAG) 8. Read FPGA Firmware Date (not JTAG)

Performance Speed of JTAG Program • File conversion takes ~2 minutes for 4Mb of configuration data • Programming PROM takes ~6.5 minutes with the SBS class set • Verifying the PROM takes ~7 minutes with the SBS class set

Console 2: MPC Menu • Includes JTAG Console and provides menu access to various MPC functions • Reading and Writing to FIFOs • Checking FIFO status • Reading and Writing CSR settings • Allows for manual and automated testing of MPC FIFOs and Sorter Logic

Inputted FIFO_A Data 18 FIFO_As Frame 1 0x???? Write 255 X Write Frame 2 0x???? 18 FIFO_As Write 1 X Frame 1 0x0000 18 FIFO_As MPC Sorter Logic Transmit Console 2: MPC Menu • The automated test runs for a specified number of iterations. For each iteration:

FIFO_B Data MPC Sorter Logic 3 FIFO_Bs Read Inputted FIFO_A Data Expected FIFO_B Data Create Console 2: MPC Menu • The automated test runs for a specified number of iterations. For each iteration:

Inputted FIFO_A Data Compares FIFO_B Data Expected FIFO_B Data Log Console 2: MPC Menu • The automated test runs for a specified number of iterations. For each iteration:

MPC Stand Alone Tests • Testing FIFOs • Wrote 255 words of random data to all FIFOs and read them back correctly • Checked that the FIFO empty and full flags were working properly • When any FIFO_A was read, that data was sent to the sorter logic • Automated Testing of Sorter Logic • In first test run found an error in MPC sorter logic. LCTs from CSC ID 2 were mistakenly identified as coming from CSC ID 3 and LCTs from CSC ID 3 were identified as coming from CSC ID 0. • Error was fixed, and MPC sorter logic has worked as expected since. • Passed 53K test iterations

MPC Stand Alone Tests • Manual Testing of Sorter Logic • Loaded each FIFO_A with different numbers of frames instead of 255 words in all 18. • Loaded vpf=1 and Quality =0 and Quality!=0 for every LCT • Loaded vpf=0 for every LCT inputted • For each possible combo of 2 out of 18 FIFOs, tested if quality the same, then it chooses the muon from highest numbered FIFO and LCT as muon 1. • Tested that sorter logic worked when FIFO_A had valid data followed by zero data and then valid data again • Tested when only put one valid muon LCT per track set, only FIFO_B1 had output and only the Muon 1 LED was on. For two valid muon LCTs, both FIFO_B1 and FIFO_B2 had output and Muon 1 & 2 LEDs were on. For three all FIFO_Bs had output and all Muon LEDs where on

MPC Performs as Expected • Only valid (vpf=1 and Quality!=0) muon LCTs are outputted • FIFO_B1 has highest Quality, FIFO_B2 has 2nd highest, FIFO_B3 has 3rd highest • If Quality is equal, then the Muon from the highest FIFO_A and LCT is given precedence • LEDs worked correctly

Console 3: TMB Menu • Provides menu access to TMB functions that are related to the MPC • Options include: • Reading in and sending a file of LCT data to the MPC • Reading LCT data sent to MPC • Reading and Writing to MPC Injector RAM Address • Reading and Writing to Injector RAM Write Data • Reading from Injector RAM Read Data • Reading and Writing to MPC Injector Control • Enable/Disable MPC Injector Start by TTC command • Read LCT Winner Bit from MPC Injector RAM • Read LCT Winner Bit from MPC Accept • Without the MPC Console, this program is very limited

Console 4: TMB & MPC Menu • Includes all of the previous consoles • Allows for manual and automated tests between the MPC, CCB, and 1 to 9 TMBs. • For an automated test run: • Can specify the number of muon frames (2 LCTs each) that are loaded into the TMBs. The number can vary for each TMB. • In each frame, every bit is randomly chosen • Can zero out the data for a specified LCT • Can specify number of test iterations

Console 4: TMB & MPC Menu • For one test iteration: LCT0 Frame 1 0x???? Inputted Muon Data 1 - 9 TMBs LCT0 Frame 2 0x???? Write 255 X Write LCT1 Frame 1 0x???? LCT1 Frame 2 0x???? MPC 1 - 9 TMBs Write 0x24 CCB

FIFO_B Data MPC Sorter Logic 3 FIFO_Bs Read Inputted Muon Data Expected FIFO_B Data Create Console 4: TMB & MPC Menu • For one test iteration:

Console 4: TMB & MPC Menu • For one test iteration: 1–9 TMB Winner Bits Inputted Muon Data Compares Expected FIFO_B Data FIFO_B Data Log

Console 4: TMB & MPC Menu • Timing of the Hard Reset of MPC and TMBs is tested • Every 20 test iterations (~7 seconds when using one TMB and the SBS class set) • Write to CCB to issue Hard Reset for All Devices • The program then reads the CCB registers to see if the configurations are done for the MPC and TMBs. • The configurations for the MPC and TMB should not be immediately done. If so, an error is logged • The MPC should be done after 40ms. If not, an error is logged • The TMB should be done after 60ms. If not, an error is logged • The program’s timer has an accuracy of 10ms in real time

1 TMB & MPC Testing • Using AddHAL class set. Loading 255 Frames. Testing Sorter Logic, 246 Winner Bit Frames per iteration, and Timing for 9K Hard Resets: • Ran 181.5K test iterations • 0 FIFO_B Errors were encountered • 0 Winner Bit Errors were encountered • 1 Hard Reset Timing Errors were encountered • Only Error was that MPC and TMB configurations were NOT DONE after 60ms and 40ms respectively. • Possible error with testing software. Originally timer started before Hard Reset command issued.

2 TMBs & MPC Testing • Testing with Two TMBs with up-to-date firmware and testing software: • Initial Error with Second TMB: Occasionally sends bit[8]=1 for LCT0 • Think possible timing error with MPC. Recompiled Firmware for New Chip • Working on finding allowed timing window

2 TMBs & MPC Testing • Using SBS class set. Loading 255 Frames in each TMB. Testing Sorter Logic, 246 Winner Bit Frames per TMB per iteration, and Hard Reset Timing for every 20 iterations: • Testing with Timing Delay of 25ns • Ran 88.0K Consecutive Test Iterations & 4.4K Hard Resets • 0 FIFO_B Errors were encountered • 0 Winner Bit Errors were encountered • 0 Hard Reset Timing Errors were encountered

2 TMBs & MPC Testing • Using SBS class set. Loading 255 Frames in each TMB. Testing Sorter Logic, 246 Winner Bit Frames per TMB per iteration, and Hard Reset Timing for every 20 iterations: • Testing with NO Timing Delay • Ran 88.0K Consecutive Test Iterations & 4.4K Hard Resets • 0 FIFO_B Errors were encountered • 0 Winner Bit Errors were encountered • 0 Hard Reset Timing Errors were encountered

TMBs & MPC Perform as Expected • Data Sent to and Passed through MPC correctly • Winner Bits are sent to TMB correctly • Hard Reset Timing is reasonable. • Only valid (vpf=1 and Quality!=0) muon LCTs inputted into TMB are outputted from MPC • FIFO_B1 has highest Quality, FIFO_B2 has 2nd highest , and FIFO_B3 has 3rd highest • If Quality is equal, then the Muon from the highest TMB and LCT is given precedence • LEDs worked correctly