Design and Verification Process: 4-bit Synchronous Register Example

E N D

Presentation Transcript

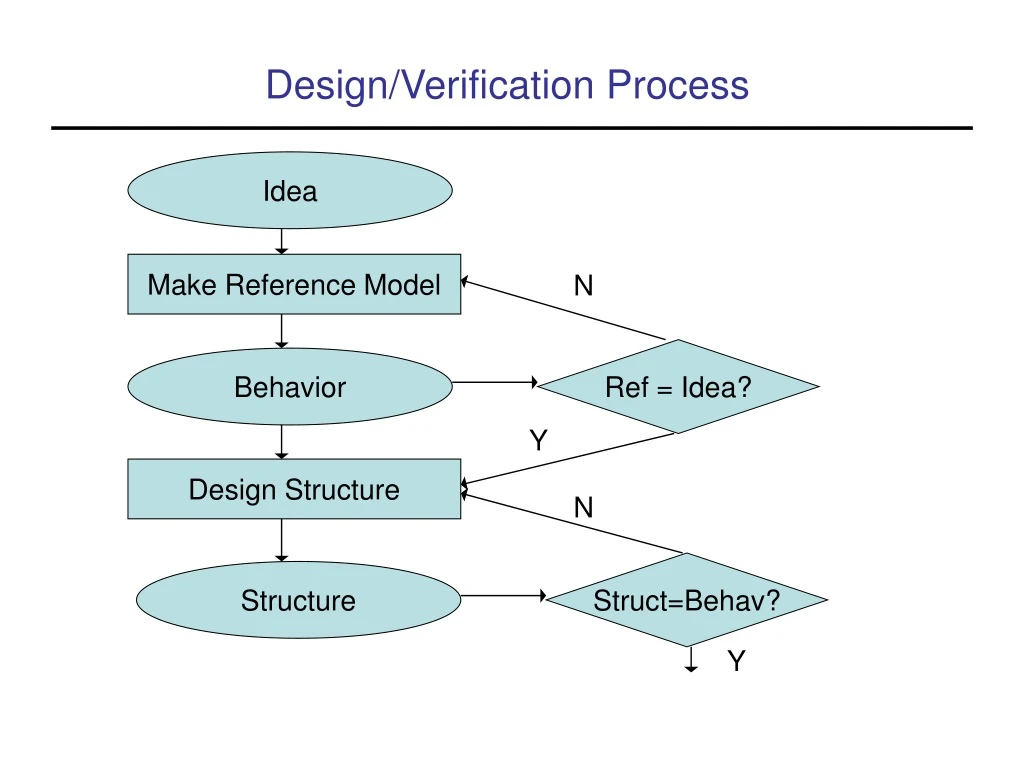

Design/Verification Process Idea Make Reference Model N Ref = Idea? Behavior Y Design Structure N Struct=Behav? Structure Y

d3 d0 d2 d1 ‘0’ ‘0’ ‘0’ ‘0’ load 00 00 00 00 01 01 01 01 10 10 10 10 clear D D D D Q Q Q Q clk q3 q2 q1 q0 Component Design/Verification Example Register, 4-bit, synchronous load and clear • Built from DFFs without load or clear • What if clear and load are both asserted?

Register, Behavioral always @(posedge load or posedge clear or posedge clock) if (load) Q <= D; else { if (clear) Q <= 4’b0; } • Load has priority over clear

Register Testbench, Response Checking reg_behav r1 (out1, in, clock, load, clear); reg_struct r1 (out2, in, clock, load, clear); always @(posedge sclock) if (out1 != out2) $display (“error”); • Sclock transitions just before clock • Outputs must settle before clock edge

Test Stimulus, Reference Model Response • 1 bit shown, assume initialized to 0 clk D Q ld clr

New Test Stimulus • 1 bit shown, assume initialized to 0 clk D Q ld clr • Is this waveform correct?

Reference Model always @(posedge load or posedge clear or posedge clock) if (load) Q <= D; else { if (clear) Q <= 4’b0; } • Load and clear are in the sensitivity list • Reset and clear are asynchronous

Testing Rules of Thumb Bad test stimulus can cause a bug to be undetected Try different relative timings on input signals