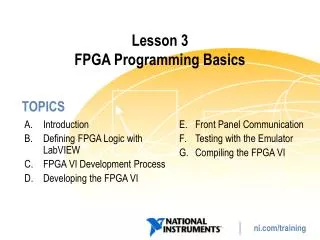

Lesson 3 FPGA Programming Basics

Lesson 3 FPGA Programming Basics. Introduction Defining FPGA Logic with LabVIEW FPGA VI Development Process Developing the FPGA VI. Front Panel Communication Testing with the Emulator Compiling the FPGA VI. A. Introduction. FPGA Layout and Components. How FPGA Works.

Lesson 3 FPGA Programming Basics

E N D

Presentation Transcript

Lesson 3FPGA Programming Basics • Introduction • Defining FPGA Logic with LabVIEW • FPGA VI Development Process • Developing the FPGA VI • Front Panel Communication • Testing with the Emulator • Compiling the FPGA VI

A. Introduction FPGA Layout and Components

How FPGA Works • Programmable interconnect switches and wires route signals in an FPGA. • Switches are known as Register Flip-Flops. • Flip-Flops pass data on a rising edge of the clock. • Compiled LabVIEW code produces a Look-up Table (LUT). • LUT defines the interconnections between configurable logic blocks (CLBs).

How FPGA Works (continued) Implements a VI that calculates a value for F from inputs A, B, C, and D where F = CD(A + B)

FPGA Family Specifications • Hardware Comparisons • Most important specification is number of logic slices • Slices help to represent the amount of logic that can implemented on a single FPGA • Ways to conserve FPGA space are covered in more detail in Lesson 8: FPGA Optimization

B. Defining FPGA Logic with LabVIEW • FPGA Module • Do not have to learn VHDL • True parallel execution • Deterministic

Compiling LabVIEW VIs to FPGA Hardware • Convert the FPGA VI into executable code • FPGA Module compiles VI • Graphical code translated to VHDL • Xilinx ISE compiler creates circuit from VHDL • Compiler optimizes the implementation • A bitstream file results • Bitstream loads at run time • Bitstream reloads at power-up • On-board flash memory • Controller over PCI Bus

Benefits of FPGA Logic in LabVIEW • FPGA provides: • Timing • Triggering • Processing • Custom I/O • Each fixed I/O uses a portion of the FPGA logic • The PCI interface also uses a portion of the FPGA logic

C. FPGA VI Development Process • Keep in mind… • No operating system on the FPGA • Download and run one top-level VI at a time • FPGA can run independently of the host • FPGA can store data • Editing a VI in the FPGA Target activates the FPGA palette • Integer math and fixed-point math

D. Developing the FPGA VI • FPGA is fast and reliable • FPGA has limited space

Demonstration • Create an FPGA VI and explore the Functions palette supported under FPGA.

E. Front Panel Communication • FPGA Front Panel • Use simple controls and indicators • Use controls and indicators only when the value will be needed on the host • Use temporary controls and indicators for debugging

Interactive Front Panel Communication (continued) • FPGA has no user interface • Must communicate data from FPGA to host PC • Requires no additional programming • Front panel displays on host PC • Block diagram executes on FPGA as compiled • Communication layer shares all control and indicator values • Cannot use debugging tools when running FPGA VI • Test with Emulator first, or add indicators as probes

F. Testing with the Emulator • Compiling—few minutes to several hours • Verify logic before compiling • LabVIEW bit-accurate emulation mode • Executes logic on the Windows PC • Traditional debugging tools are available • Two kinds of emulation • Random data for inputs • Target hardware for I/O

Using the Emulator • Right-click the FPGA Target in the Project Explorer window and select Properties. • Select General. • Select an Emulator option. • Click OK. • Run the VI. • *Set the Emulator to Off after test

Exercise 3-1: Creating a LabVIEW FPGA VI • Create a VI that adds two numbers and runs a benchmark in parallel that determines how fast code is running. • Run the VI in emulation mode and use debugging tools.

G. Compiling the FPGA VI • Click Run • Converts graphical code to VHDL • Generates intermediate files

Compiling VI for FPGA Dialog Box • Disconnect – Disconnects from the Compile Server so that you can continue working in LabVIEW • Follow instructions in the dialog box to reconnect

LabVIEW FPGA Compile Server Dialog Box • Tools»FPGAModule»Start Local Compile Server to view previous compile reports • Click Compile List

Exercise 3-2: Compile a LabVIEW FPGA VI • Compile the application created in Exercise 3-1.

Summary—Quiz • 1. The FPGA VI runs in an operating system on the FPGA processor. a. True b. False • 2. You must know VHDL programming to reconfigure the FPGA. a. True b. False

Summary—Quiz • 3. The FPGA can achieve true, simultaneous parallel processing of parallel operations. a. True b. False • 4. Interactive Front Panel Communication runs the front panel on the Windows PC and the circuit configured from the block diagram on the FPGA. a. True b. False