CA Final Project – Multithreaded Processor with IPC Interface

CA Final Project – Multithreaded Processor with IPC Interface. Part I – Project Review. Goal. Multicore processors, e.g. the TI OMAP and the IBM Cell, are getting more and more popular either in the multimedia or the communication applications

CA Final Project – Multithreaded Processor with IPC Interface

E N D

Presentation Transcript

CA Final Project – Multithreaded Processor with IPC Interface Part I – Project Review

Goal • Multicore processors, e.g. the TI OMAP and the IBM Cell, are getting more and more popular either in the multimedia or the communication applications • However, the processors are usually underutilized due to some latency • IPC latency • Pipeline latency • Memory latency • In this project, the studentsare requested to come up with somesolutions to those latency and evaluate the effectiveness

Experiment Environment • ARM Versatile platform • Host processor (ARM926) • DSP accelerator (MIPS compatible) on the FPGA • Baseline (1 thread), 40MHz • IMT (4 threads), 10MHz • Applications • JPEG decoder (VGA-sized)

Grading • Evaluate the DSP utilization in the following cases (the same IPC mechanism) • Multithreaded DSP • MPU handles the IPC (software solution) • DSP handles the IPC (hardware solution) • MPU handles the IPC • Single-threaded DSP • Multithreaded DSP • Explain what is the most critical overhead in your dual-core processor experiment • Explain whether the IMT-DSP is the good solution to reduce the overhead in your experiment

Reference • S. H. Ou, T. J. Lin, X. S. Deng, Z. H. Zhuo, and C. W. Liu, “Multithreaded coprocessor interface for multicore multimedia SoC, ” in ASPDAC, 2008

Outline • Environment setting • Coding on the CodeWarrier • Burn design on the FPGA

Software Required • Xilinx ISE (v9.1i) • ARM Multi-ICE (v2.2) • ARM Developer Suite (v1.2)

Xilinx ISE • Install CD1 (main program) • Install CD2 (FPGA model) • Virtex 2 should be included

Multi-ICE • Install Multi-ICE and its patch • The patch contains ARM926EJ-S data • Connect versatile and run “Multi-ICE Server”, 2 mode will be found • Normal mode (config jumper open) • Config mode (config jumper closed)

ARM Developer Suite • Install • Run Multi-ICE first (In normal mode) • Run AXD Server and config as follows: • Option->Configure Target->Add • choose Multi-ICE\Multi-ICE.dll • Configure->select ARM926EJ-S • Load Image and start debug

Create a “New Project” Include the source code and other files Example

Platform environment settings Select “Make” to generate *axf file and “Run” to run on the ARM926 Example 1. Make Run choose ARM926EJ-S include DMA.scf 2.

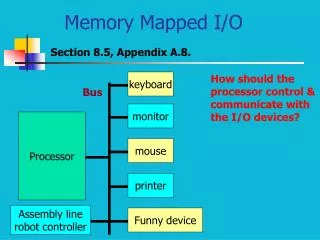

AMBA bus connection Address decode AMBA Bus Protocol

RTL codes on Xilinx Project Navigator – Implementation • Translate • Merge multiple design files into a single netlist • Map • Group logical symbols from the netlist (gates) into physical components (slices and IOBs) • Place & Route • Place components onto the chip, connect them, and extract timing data into reports

Wrap your design with a wrapper Generate BIT file Example wrapper your design Click “Generate Programming File”

Multi-Ice mode selection Burn Boardfiles -> progcards_multiice.exe Example

Example • ARM-FPGA co-process