Advanced Placement and Routing Techniques in FPGA Design

This guide explores advanced placement and routing methodologies used in FPGA design, focusing on cost optimization through techniques like greedy placement, simulated annealing, and order-independent routing. We discuss the importance of minimizing wirelength and congestion, outlining the implementation of algorithms that address local minima issues. The use of cooling schedules and acceptance criteria in simulated annealing is also covered to enhance placement quality. Readers will gain insights into effective strategies for managing chip locations for logic blocks to optimize performance.

Advanced Placement and Routing Techniques in FPGA Design

E N D

Presentation Transcript

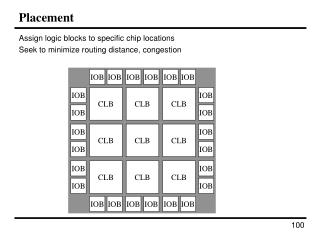

CLB CLB CLB CLB CLB CLB IOB IOB IOB IOB IOB IOB CLB CLB CLB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB Placement • Assign logic blocks to specific chip locations • Seek to minimize routing distance, congestion

Placement Cost Function - Wirelength • Most systems use Manhattan routing (North, South, East, West, no diagonals) • Wirelength estimate = 1/2*(perimeter of bounding box) = “Semi-perimeter” A1 C3 B3 A2 C2 B2 C1 B1

D A C B Greedy Placement • Create initial placement randomly • old_cost = cost(placement); • for (iteration = 0; iteration < max_iteration; iteration++) { • swap random pair of logic blocks; • new_cost = cost(placement); • if (old_cost < new_cost) • undo_move(); • }

d3 d4 a1 a2 D A d2 a3 d3 c2 d4 c1 b4 a1 b3 a2 A B d2 a3 d1 a4 d1 a4 b1 c4 b1 c4 D C C B b2 c3 b2 c3 c2 c1 b4 b3 Placement Local Minima • Greedy placement algorithms (force-directed, recursive bipartitioning) can easily get stuck in local minima • Need a method that is less susceptible to local minima

Annealing • Annealing: Cooling hot metals to form good crystal structures • Start at high temperatures - atoms move randomly about • Cool at specific cooling schedule - leave enough time for atoms to attract into crystal lattice

Simulated Annealing • Move nodes randomly • Initially “high temperature” - allow bad moves to happen • Lower temperature, accepting less and less bad moves • Slowly “cool” placement to allow good structure to form Cost Possible Placements

SA Acceptance Criteria & Cooling Schedule • Compute delta = cost(old_placement) - cost(new_placement) • if (delta>=0) accept • else if ( ) accept, else reject /* 0<=random<=1 */ • Initially temperature is very high (most bad moves accepted) • Temp slowly goes to 0, with multiple moves attempted at each temperature • Final runs with temp=0 (always reject bad moves) greedily “quench” the system

SA Cost Function • Simulated Annealing requires a cost function that captures quality of placement • Smaller cost means better placement • Multiple concerns captured in one metric INV NOR DFF NAND

Simulated Annealing Algorithm • Create initial placement randomly • old_cost = cost(placement); • for (temp = max_temp; temp >= min_temp; temp = next_temp) { • for (iteration = 0; iteration < max_iteration; iteration++) { • swap random pair of logic blocks; • new_cost = cost(placement); • if (old_cost < new_cost) • if (random >= Func((old_cost - new_cost)/temperature)) • undo_move(); • } • }

CLB CLB CLB CLB CLB CLB IOB IOB IOB IOB IOB IOB CLB CLB CLB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB IOB Routing • Assign logic blocks to specific chip locations • Seek to minimize routing distance, congestion

Route together all the A’s, and all the B’s, minimizing the amount of metal Dark areas are impassible barriers A B A B A A

Maze Router • Breadth-first search along “wavefront”

Maze Routing Acceleration: A*/Detour Numbers • Cost of each location includes minimum distance to destination

Greedy Multi-terminal Routing • Route until first terminal found. • Unmark all nodes. Nodes on previous path marked as 1. Continue routing

1 2 2 1 4 4 Order Independent Routing • Can avoid order dependency by iterating: • Until good routing found { • Route nets independent of congestion • Add “penalty” to over-capacity regions • } A B C D E 3 F G H 3 I J K L M N O P Q R S T U V W