Overview of Experimental 256Mb Non-Volatile DRAM for Advanced VLSI Course

This presentation by Sheis Abolma’ali discusses the development and characteristics of a 256Mb Non-Volatile DRAM (NVDRAM) with an innovative cell plate boosted programming technique, as presented at ISSCC 2004. The outline covers various aspects, including the introduction to non-volatile memories, NVDRAM cell structure, operation modes, and advantages over traditional memories like FLASH and EEPROM. The potential of NVDRAM in reducing power consumption and enhancing endurance is highlighted, demonstrating its viability for future memory technologies.

Overview of Experimental 256Mb Non-Volatile DRAM for Advanced VLSI Course

E N D

Presentation Transcript

An Experimental 256Mb Non-Volatile DRAMClass presentation for Advanced VLSI coursepresented by : Sheis Abolma’aliWinter 2004 Major reference is : An Experimental 256Mb Non-Volatile DRAMwith Cell Plate Boosted Programming Technique By : J-H. Ahn, S-H. Hong, S-J. Kim, J-B. Ko, S-W. Shin, S-D. Lee, … Hynix Semiconductor Inc. , Seoul National University In “ISSCC 2004” , presented at “February 16th”

Outline • Introduction to Non-Volatile Memories - Memory technologies and usage - A simple cell structure • NVDRAM Memory Cell - Cell Structure - Comparison to other memories • NVDRAM Operation - Operation Modes - Prototype Chip Architecture • Advantages and Conclusions

Memory Technologies and their disadvantages • PROMs (EPROM, EEPROM) - EPROM should erase off-chip - EEPROM has larger area • Flash Memory - Consumes too much power for Program/Erase operation - Slow write speed, Program/Erase endurance problem • FeRAM, MRAM - Process is not matured, New materials are necessary • DRAM - Volatile

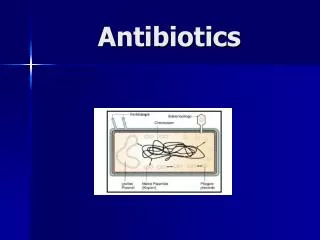

A Flash Memory Cell Control gate Floating gate BL Erasure Thin tunneling oxide (10 nm) WL n+ source n+ drain Programming P-substrate Device A Cell

What is NVDRAM? • Cell structure is similar to DRAM - Almost same cell structure as DRAM (1T1C) - Cell transistor has non-volatile storage capability • Non-volatility is valid only for chip power-off state - Program is performed only when power goes off (Power off detection circuit is used) - Erase is performed only when power goes on (Temporary backup memory is used) • Program/Recall occurs inside of the cell - Program moves the capacitor data to the transistor - Recall moves the transistor Vt shift to the capacitor

NVDRAM Memory Cell Why SONOS ? Scaling, ease of integration in a base line CMOS process, ease of manufacturing

Advantages of NVDRAM • Power Efficiency - No Program/Erase operation during power on state - All cells are programmed or erased together - DRAM capacitor charges are used for programming • No Program/Erase disturb from other cells - Cell Plate Stress is used for programming. No bit line stress! - Erasing saturates the Cell Vt to the max. value No disturb and no over-erasing issue • Endurance - No electrical field is applied to the programmed cells

Conclusions • Demonstrated non-volatile DRAM operation • Cell constructed with a same DRAM feature size • Cell transistor has SONOS structure feasible for low voltage operation • Program operation from the cell capacitor side with boosted cell plate voltage • Block by block erase operation with back up memory • Long endurance since non-volatile mode is only used in power off state

References • J-H. Ahn, ” An Experimental 256Mb Non-Volatile DRAMwith Cell Plate Boosted Programming Technique,” ISSCC Dig. Tech Paper, pp. presentation, Feb. 2004. • J-M Rabaey, “Digital Integrated Circuits: A Design Perspective, Second Edition”, Chapter 12: Designing Memory and Array Structure, Prentice Hall Publication