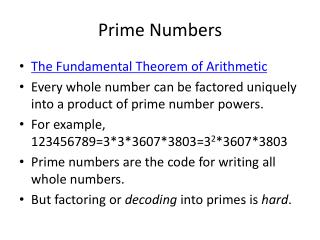

Prime Numbers

Prime Numbers. Lecture L6.1 Sieve of Eratosthenes. j 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15. Find prime numbers using Sieve of Eratosthenes. 1. 1. 1. 1. 1. // first create an array of flags, where // each member of the array stands for a odd number

Prime Numbers

E N D

Presentation Transcript

Prime Numbers Lecture L6.1 Sieve of Eratosthenes

j 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Find prime numbers using Sieve of Eratosthenes 1 1 1 1 1 // first create an array of flags, where // each member of the array stands for a odd number // starting with 3. for (j = 0; j < size; j++) { flags[j] = 1; } 1 1 1 1 1 1 1 size = 1024 1 1 1 1

Find prime numbers using Sieve of Eratosthenes j 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 • a b • 3 3 • 5 6 • 7 9 • 9 12 • 15 • 13 18 • 15 21 • 17 24 • 19 27 • 21 30 • 23 33 • 25 36 • 27 39 • 29 42 • 31 45 • 33 48 1 1 primeCount = 0; for (j = 0; j < size; j++) { if (flags[j] == 1) { // found a prime, count it primeCount++; // now set all of the multiples of // the current prime number to false // because they couldn't possibly be prime a = 2*j + 3; // odd numbers starting with 3 b = a + j; while(b < size) { flags[b] = 0; b = b + a; } } } 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Find prime numbers using Sieve of Eratosthenes j 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 • a b • 3 3 • 5 6 • 7 9 • 9 12 • 15 • 13 18 • 15 21 • 17 24 • 19 27 • 21 30 • 23 33 • 25 36 • 27 39 • 29 42 • 31 45 • 33 48 1 1 primeCount = 0; for (j = 0; j < size; j++) { if (flags[j] == 1) { // found a prime, count it primeCount++; // now set all of the multiples of // the current prime number to false // because they couldn't possibly be prime a = 2*j + 3; // odd numbers starting with 3 b = a + j; while(b < size) { flags[b] = 0; b = b + a; } } } 1 0 1 1 1 1 1 1 1 1 1 1 1 1

Find prime numbers using Sieve of Eratosthenes j 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 • a b • 3 3 • 5 6 • 7 9 • 9 12 • 15 • 13 18 • 15 21 • 17 24 • 19 27 • 21 30 • 23 33 • 25 36 • 27 39 • 29 42 • 31 45 • 33 48 1 1 primeCount = 0; for (j = 0; j < size; j++) { if (flags[j] == 1) { // found a prime, count it primeCount++; // now set all of the multiples of // the current prime number to false // because they couldn't possibly be prime a = 2*j + 3; // odd numbers starting with 3 b = a + j; while(b < size) { flags[b] = 0; b = b + a; } } } 1 0 1 1 0 1 1 1 1 1 1 1 1 1

Find prime numbers using Sieve of Eratosthenes j 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 • a b • 3 3 • 5 6 • 7 9 • 9 12 • 15 • 13 18 • 15 21 • 17 24 • 19 27 • 21 30 • 23 33 • 25 36 • 27 39 • 29 42 • 31 45 • 33 48 1 1 primeCount = 0; for (j = 0; j < size; j++) { if (flags[j] == 1) { // found a prime, count it primeCount++; // now set all of the multiples of // the current prime number to false // because they couldn't possibly be prime a = 2*j + 3; // odd numbers starting with 3 b = a + j; while(b < size) { flags[b] = 0; b = b + a; } } } 1 0 1 1 0 1 1 0 1 1 1 1 1 1

Find prime numbers using Sieve of Eratosthenes j 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 • a b • 3 3 • 5 6 • 7 9 • 9 12 • 15 • 13 18 • 15 21 • 17 24 • 19 27 • 21 30 • 23 33 • 25 36 • 27 39 • 29 42 • 31 45 • 33 48 1 1 primeCount = 0; for (j = 0; j < size; j++) { if (flags[j] == 1) { // found a prime, count it primeCount++; // now set all of the multiples of // the current prime number to false // because they couldn't possibly be prime a = 2*j + 3; // odd numbers starting with 3 b = a + j; while(b < size) { flags[b] = 0; b = b + a; } } } 1 0 1 1 0 1 1 0 1 1 0 1 1 1

Find prime numbers using Sieve of Eratosthenes j 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 • a b • 3 3 • 5 6 • 7 9 • 9 12 • 15 • 13 18 • 15 21 • 17 24 • 19 27 • 21 30 • 23 33 • 25 36 • 27 39 • 29 42 • 31 45 • 33 48 1 1 primeCount = 0; for (j = 0; j < size; j++) { if (flags[j] == 1) { // found a prime, count it primeCount++; // now set all of the multiples of // the current prime number to false // because they couldn't possibly be prime a = 2*j + 3; // odd numbers starting with 3 b = a + j; while(b < size) { flags[b] = 0; b = b + a; } } } 1 0 1 1 0 1 1 0 1 1 0 1 1 0

Find prime numbers using Sieve of Eratosthenes j 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 • a b • 3 3 • 5 6 • 7 9 • 9 12 • 15 • 13 18 • 15 21 • 17 24 • 19 27 • 21 30 • 23 33 • 25 36 • 27 39 • 29 42 • 31 45 • 33 48 1 1 primeCount = 0; for (j = 0; j < size; j++) { if (flags[j] == 1) { // found a prime, count it primeCount++; // now set all of the multiples of // the current prime number to false // because they couldn't possibly be prime a = 2*j + 3; // odd numbers starting with 3 b = a + j; while(b < size) { flags[b] = 0; b = b + a; } } } 1 0 1 1 0 1 1 0 1 0 0 1 1 0

primeCount = 0; for (j = 0; j < size; j++) { if (flags[j] == 1) { primeCount++; a = 2*j + 3; b = a + j; while(b < size) { flags[b] = 0; b = b + a; } } } Sieve of Eratosthenes Datapath

Sieve of Eratosthenes Control Unit primeCount = 0; for (j = 0; j < size; j++) { if (flags[j] == 1) { primeCount++; a = 2*j + 3; b = a + j; while(b < size) { flags[b] = 0; b = b + a; } } }

countg.vhd library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity countg is generic(width:positive); port ( inc: in STD_LOGIC; clr: in STD_LOGIC; clk: in STD_LOGIC; q: out STD_LOGIC_VECTOR (width-1 downto 0) ); end countg;

countg.vhd (cont.) architecture countg_arch of countg is signal q1: STD_LOGIC_VECTOR(width-1 downto 0); begin process(clk, clr) begin if clr = '1' then for i in width-1 downto 0 loop q1(i) <= '0'; end loop; elsif (clk'event and clk = '1') then if inc = '1' then q1 <= q1 + 1; end if; end if; end process; q <= q1; end countg_arch;

j2p3.vhd -- Title: j2p3 library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity j2p3 is generic(width:positive); port ( j: in STD_LOGIC_VECTOR(width-1 downto 0); y: out STD_LOGIC_VECTOR(width-1 downto 0) ); end j2p3; architecture j2p3_arch of j2p3 is begin jp1: process(j) begin y <= (j(width-2 downto 0) & '0') + 3; end process jp1; end j2p3_arch;

lessthan.vhd library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity lessthan is generic(width:positive); port ( a: in STD_LOGIC_VECTOR(width-1 downto 0); b: in STD_LOGIC_VECTOR(width-1 downto 0); a_lt_b: out STD_LOGIC ); end lessthan; architecture lessthan_arch of lessthan is begin alb1: process(a, b) variable Z: STD_LOGIC; begin if (a < b) then a_lt_b <= '1'; else a_lt_b <= '0'; end if; end process alb1; end lessthan_arch;

Project -> New Source… -> Coregen IP File Name: flagsm Double-click

soedp.vhd -- Title: Sieve of Erostostones Datapath library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.std_logic_unsigned.all; use work.soe_components.all; entity soedp is port( clk : in STD_LOGIC; clr : in STD_LOGIC; aload, bload, m1sel, fload, reset : in STD_LOGIC; pinc, cinc, jinc : in STD_LOGIC; jf, bf: out std_logic; f : out STD_LOGIC_VECTOR(0 downto 0); pcount : out STD_LOGIC_VECTOR(15 downto 0); ccount : out STD_LOGIC_VECTOR(19 downto 0) ); end soedp;

soedp.vhd (cont.) architecture soedp_arch of soedp is signal a1, a, j, b, k, s, size: std_logic_vector(15 downto 0); signal zero: std_logic_vector(0 downto 0); constant bus_width: positive := 16; constant ccount_width: positive := 20; begin size <= "0000010000000000"; -- 1024 zero <= "0"; U1: adder generic map(width => bus_width) port map (a => k, b => a, y => s); M1: mux2g generic map(width => bus_width) port map (a => b, b => j, sel => m1sel, y => k); Ra: regc generic map(width => bus_width) port map (d => a1, load =>aload, reset => clr, clk =>clk, q => a); Rb: regc generic map(width => bus_width) port map (d => s, load => bload, reset => clr, clk =>clk, q => b);

soedp.vhd (cont.) Rj: countg generic map(width => bus_width) port map (inc => jinc, clr => clr, clk =>clk, q => j); U2: j2p3 generic map(width => bus_width) port map (j => j, y => a1); U3: lessthan generic map(width => bus_width) port map (a => j, b => size, a_lt_b => jf); U4: lessthan generic map(width => bus_width) port map (a => b, b => size, a_lt_b => bf);

soedp.vhd (cont.) nprime: countg generic map(width => bus_width) port map (inc => pinc, clr => clr, clk =>clk, q => pcount); ccycles: countg generic map(width => ccount_width) port map (inc => cinc, clr => clr, clk =>clk, q => ccount); flgq : flagsm -- Logicore port map ( addr => k(9 downto 0), clk => clk, din => zero, dout => f, we => fload); end soedp_arch;

-- Title: Seive of Erostothenes Control Unit library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity soe_control is port ( clr: in STD_LOGIC; clk: in STD_LOGIC; jf, bf: in STD_LOGIC; f : in STD_LOGIC_VECTOR(0 downto 0); pinc, cinc, jinc: out STD_LOGIC; aload, bload, m1sel, fload, reset: out STD_LOGIC ); end soe_control; architecture soe_control_arch of soe_control is type state_type is (s0, s1, s2, s3, s4, s5, s6, s7, s8); signal current_state, next_state: state_type; begin soe_control.vhd

soe_control.vhd (cont.) C1: process(current_state, jf, bf, f) begin case current_state is when s0 => next_state <= s1; when s1 => if jf = '1' then next_state <= s2; else next_state <= s8; end if; when s2 => if f = "0" then next_state <= s3; else next_state <= s4; end if;

soe_control.vhd (cont.) when s3 => next_state <= s1; when s4 => next_state <= s5; when s5 => if bf = '1' then next_state <= s7; else next_state <= s6; end if; when s6 => next_state <= s1; when s7 => next_state <= s5; when s8 => next_state <= s8; end case; end process C1;

soe_control.vhd (cont.) statereg: process(clk, clr) -- the state register begin if clr = '1' then current_state <= s0; elsif (clk'event and clk = '1') then current_state <= next_state; end if; end process statereg;

soe_control.vhd (cont.) C2: process(current_state, bf, f) begin -- Initialize all outputs pinc <= '0'; cinc <= '1'; jinc <= '0'; aload <= '0'; bload <= '0'; m1sel <= '0'; fload <= '0'; reset <= '0';

soe_control.vhd (cont.) case current_state is when s0 => -- reset ccycles and flags reset <= '1'; when s1 => m1sel <= '1'; -- f <- flag(j) when s2 => -- f <- flag(j) m1sel <= '1'; if f = "1" then -- pcount++ pinc <= '1'; else -- j++ jinc <= '1'; end if; aload <= '1'; -- a <- 2j+3 when s3 => -- null null;

soe_control.vhd (cont.) when s4 => m1sel <= '1'; -- b <- a + j bload <= '1'; when s5 => if bf = '1' then fload <= '1'; -- flag(b) <- '0' m1sel <= '0'; bload <= '1'; -- b <- b + a else -- j++ jinc <= '1'; end if;

soe_control.vhd (cont.) when s6 => -- null null; when s7 => -- null null; when s8 => -- null cinc <= '0'; when others => null; end case; end process C2; end soe_control_arch;

prime.vhd -- Title: Prime numbers using Sieve of Erostostones library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.std_logic_unsigned.all; use work.prime_components.all; entity prime is port( mclk : in STD_LOGIC; bn : in STD_LOGIC; BTN4 : in STD_LOGIC; led: out std_logic; ldg : out STD_LOGIC; LD : out STD_LOGIC_VECTOR(1 to 8); AtoG : out STD_LOGIC_VECTOR(6 downto 0); A : out STD_LOGIC_VECTOR(3 downto 0) ); end prime;

prime.vhd (cont.) architecture prime_arch of prime is signal jf, bf: std_logic; signal f: std_logic_vector(0 downto 0); signal clr, clk, cclk, bnbuf: std_logic; signal clkdiv: std_logic_vector(26 downto 0); signal r, p : STD_LOGIC_VECTOR(15 downto 0); signal pinc, cinc, jinc: STD_LOGIC; signal aload, bload, m1sel, fload, reset: STD_LOGIC; signal pcount : STD_LOGIC_VECTOR(15 downto 0); signal ccount : STD_LOGIC_VECTOR(19 downto 0); constant bus_width: positive := 16; begin U00: IBUFG port map (I => bn, O => bnbuf); led <= bnbuf; ldg <= '1'; -- enable 74HC373 latch clr <= bnbuf;

prime.vhd (cont.) -- Divide the master clock (50Mhz) process (mclk) begin if mclk = '1' and mclk'Event then clkdiv <= clkdiv + 1; end if; end process; clk <= clkdiv(0); -- 25 MHz cclk <= clkdiv(17); -- 190 Hz U1: soedp port map (clk => clk, clr => clr, aload => aload, bload => bload, m1sel => m1sel, fload => fload, reset => reset, pinc => pinc, cinc => cinc, jinc => jinc, jf => jf, bf => bf, f => f, pcount => pcount, ccount => ccount);

prime.vhd (cont.) U2: soe_control port map (clk => clk, clr => clr, aload => aload, bload => bload, m1sel => m1sel, fload => fload, reset => reset, pinc => pinc, cinc => cinc, jinc => jinc, jf => jf, bf => bf, f => f); M1: mux2g generic map(width => bus_width) port map (a => pcount, b => ccount(15 downto 0), sel => BTN4, y => r); U3: binbcd port map (B => r, P => p); U4: x7seg port map (x => p, cclk => cclk, clr => clr, AtoG => AtoG, A => A); LD(1 to 4) <= ccount(19 downto 16); end prime_arch;