第四章 8086 的总线操作和时序

第四章 8086 的总线操作和时序. 二、 CPU 的时序和存储器及外设的时序. 参见 P171 图 5-7 8086CPU. T1:A19-A16( 锁存)、 AD15-AD0 (锁存) T2:CPU 发出读信号 T3-T4 下降沿,采样数据总线 D15-D0 获取数据总线周期结束 CPU 读存储器时序,不管 M 接到地址和读命令信号后,能否在 T4 前沿把数据送至数据总线 配合问题是 ready 线( M /IO 输给 CPU 状态线 ) T3 状态的下降沿采样 ready 信号:

第四章 8086 的总线操作和时序

E N D

Presentation Transcript

二、CPU的时序和存储器及外设的时序 • 参见P171图5-7 8086CPU

T1:A19-A16(锁存)、AD15-AD0(锁存) T2:CPU发出读信号 T3-T4下降沿,采样数据总线D15-D0获取数据总线周期结束 CPU读存储器时序,不管M接到地址和读命令信号后,能否在T4前沿把数据送至数据总线 配合问题是ready线( M /IO输给CPU状态线) T3状态的下降沿采样ready信号: 若M或I/O能在T4状态前沿前把数据送至数据总线,ready为一,CPU在T3状态以后进入T4状态,采样数据,总线周期结束。 若M或I/O 不能在T4状态前把数据送至数据总线,则ready为0,CPU在T3状态结束插入TW(且保持采样ready),若ready=1,TW结束,CPU进入T4,采样数据,结束总线周期。 目的:1)了解指令执行过程 2)选用指令,缩短M和执行时间 MOV AX, 0 4个T SUB AX, AX XOR AX,AX 3个T

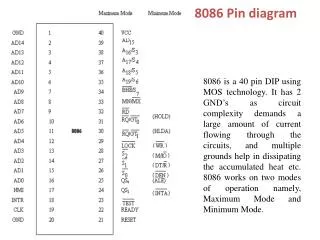

3)时序配合(CPU、IO/M) 4) 估计CPU完成操作所需的时间 第二节 8086的总线 一、8086的两种组态:最小组态 图5-1 最大组态图5-2 地址总线:A19~A0 8282(锁存器) BUS: 数据总线:AD0~AD15或8286(发送/接收接口片) 控制总线:CPU供给的控制线提供 8088通过总线控制器。 8288形成两种总线, 控制信号由8288提供 由8086的引脚MN/MX=1 最小组态 MN/MX=0 最大组态 (一)最小组态 引脚24到31的意义: 28脚IO/M:区分是存储器访问还会是I/0访问 若为0 高电平 I/O访问 为1位存储器访问 浮空时 CPU处DMA响应(外设←→M)

29脚 WR(输出,三态) 低电平有效,CPU在写操作时输出的一个选项信号,表示是处在(IO/M)写周期(在T2、T3、TW)状态有效 CPU在DMA响音时,此线浮空。 24脚 INTA(输出):CPU输出的中断响应信号 0有效 在T2、T3、TW状态有效,可用作中断矢量的读选通信号 25脚 ALE(输出):地址锁存允许信号 在T1状态位低时,由CPU提供正选通脉冲 把在(AD0~AD15)和地址—状态A16-A9上的地址信号锁存在地址锁存器(8282/8283)中 27脚 DT/R(输出、三态):数据发送/接受信号 在最小组态时,为增强数据总线的驱动能力,我们8286、8287需要DT/R,以确定数据传送的方向。 高:数据发送(CPU写);低:接受信号(CPU读)。DMA时,此线浮空。 26脚 DEN(输出,三态):数据允许信号,低电平有效 在使用8286/8287的最小组态系统中,此信号作8286/8287输出允许信号,在访问M、IO或中断响应周期有效,DMA时,浮空。 31脚 HOLD(输入):总线请求信号 30脚 HLDA(输出):总线请求响应信号

HOLD:系统中别的总线设备要求占用总线,向CPU发出总线请求信号,1有效,当CPU收到HOLD请求后,在T4状态输出一个高电平有效的总线请求响应信号HLDA。同时,CPU使地址线,数据线和相应的控制信号线浮空。HOLD:系统中别的总线设备要求占用总线,向CPU发出总线请求信号,1有效,当CPU收到HOLD请求后,在T4状态输出一个高电平有效的总线请求响应信号HLDA。同时,CPU使地址线,数据线和相应的控制信号线浮空。 当HOLD=0,则HLDA=0,同时又控制总线。 SSO 系统状态信号,与IO、M、DT/R P163表5-1(反映此行总线周期的状态) (二)最大组态 引脚24-31 T4状态的变化,表示总线周期开始 P163表5-2 S2、S1、S0(输出、三态) 这些信号由总线控制器用以产生M、IO的总线周期和所需的控制信号 31脚 RQ/GT0 30脚 RQ/GT1(输入/输出)请求允许脚请求、允许顺序:(外部的总线设备) (1)其他总线在设备实发宽度为一个时钟周期的脉冲给CPU表示总线请求HOLD (2)CPU在T4或下一次T4输出宽度为一个时钟周期的脉冲给请求总线的设备作为总线响应信号 HLDA (3)在DMA结束时,总线请求设备输出脉冲给CPU总线请求结束。CPU又控制总线。

29脚 LOCK(输出、三态) 在其有效时,别的总线主设备不能获得对总线的控制,由前缀指令“LOCK” 使其有效,在下一个指令完成以前保持有效。 QS1、QS0(输出) P164 表5-3 提供一种状态允许外部追踪8086内部的指令 二 8086的引线 AD15-AD0(输入/输出三态) 低16位地址线和低16位数据线公用,从时间上加以区分。 CPU访问M、IO,先给出T1状态地址,通过地址锁存器锁存地址。 在T2、T3、TW状态读写数据。 A15~A0(输出,三态) 低16位地址线 A19/S6,A18/S5,A17/S4,A16/S3(输出,三态) T1状态锁存地址(最高4位地址) T2.T3.TW作为状态信息 S6始终为零,S5为F中的中断允许标志位。 S4.S3段寄存器有四个状态, P164 表5-4 DMA 此线浮空 RD(输出,三态) 为其有效时,表示正在进行M.I/O读

ready(输入) M/IO输出,CPU在T3周期采样ready线,若ready(输入) 若ready=0, T3后插入TW,直到ready有效 进入T4,完成数据传送 INTR(输入)18引脚 可屏蔽中断请求信号 高电平有效 CPU在每一个指令周期最后一个T状态采样决定是否进入中断响 应周期(软件可屏蔽) 中断允许位加以屏蔽 TEST输入 23引脚 当TEST=1,wait指令等待;TEST=0,执行继续。 NMI(输入) 非屏蔽输入信号(不能软件加以屏蔽) 由低到高,在先行指令结束以后引起中断。 RESET(输入) 21引脚 复位输入引起处理器立即结束先行操作 CLK(输入) 时钟输入信号 GND 地线 VCC 电源

第三节 8086典型的时序分析 8088最基本的总线周期是CPU与M、I/O进行通信 一、存储器读周期 P21 如图4-7 存储器读时序图 (1)T1:确定M、I/O(在T1)状态 (2)确定单元的地址:T1状态开始,20位地址读出,A19~A16,A15~A0 ,锁存到8282存储器 T2状态:S0~S3 三态 (3)给出读命令:RD信号在T2状态变为有效(WR无效) 地址信号→译码→指定单元→若干时候后→内容出现在数据线D15-D0 如果启用8286(发送、接受),有DT/R和DEN T2:DT/R为低电平,PEN也在为低(选通信号) T4:CPU在下降沿采样数据线获得数据 若M、I/O在T3状态的下降沿ready=0,则在T3后插入若干个TW状态(一个时钟周期)只有ready=1,才TW结束后进入T4 二、存储器写周期

1)~2)同上 3)要写入存储器的数据,在T2状态。A15-A0已由AIE锁存 CPU就要写入的8位数据,放至AD7~AD0数据线上,DT/R=1 4)8088在T4状态后使控制信号无效。 即在T4状态,完成对M、I/O的写入过程 DT/R 在T2-T4为高电平。DEN、T2后为低电平。 三、输入输出周期 当CPU与外设交换信息(就要用到输入或输出指令),即从外设输入数据,或把 数据输出给外设的时序与CPU通M通信的时序相似。 四、空转周期 若CPU不执行机器周期,则总线接口执行空转周期(系列T1状态),CPU在高位地址线保持一个机器周期的状态信息。 五、中断响应周期 INTR CPU I=1(CPU开中断) NMI CPU在当前指令 执行完毕后,响应中断。

六、系统复位reset 当CPU在reset线上检测一个正脉冲时(复位时) 码段寄存器 FFFFH=CS=FFFFH 指令指针 IP=0000H ES=DS=0000 SS=0000 I=0 在复位时,系统对INTR时屏蔽的,用软件使STL,使I=1开中断 reset高电平,必须持续至少四个时钟周期 地址总线浮空,直至CPU脱高复位状态,开始从FFFFOH单元取指令(而 FFFF0有效,JMP以便转移至程序的实际开始处。) 七、CPU进入和退出保持状态的时序CPU接收同步HOLD信号,在T4或T1后段输出保 持响应HLDA,从下一时钟开始CPU让出总线 当外设DMA(直接数据通道传送)DMA结束后,使HOLD无效,则在下一个时钟 HLDA到低电平。 8282 8286 8288 锁存器 数据发送/接受 总线控制器 ALE DT/R

第四节 最大组态下的8088时序 T1:8088将发出20位地址信号锁存,将S0、S1、S2送给总线控制器,再输出到地址总线(对S0~S2译码后,锁存地址,判断位读操作,DT/R=0) T2:将地址切换到数据线D7-D0,发读存储器命令MRDC 控制器,8288发出DEN=0信号,使数据总线与8088数据总线接通,同时,A19/S0 -A16/S3切换位状态信息。 T3:8088采样ready Ready=1 进入T4 0 在T3后插入TW 总线周期结束 (T4之前的时钟上升沿)8088发出S0~S2为111,为执行下一个总线周期作准备 一、存储器读周期和写周期 T1:判断写操作DT/R=0 T2:8288发出AMNC命令(写命令),在DEN=0(有效),使8088输出数据,经过数据收发器送到数据总线 T3:8088采样ready= 1 0 读 写 DATA T3 T2 状态

二、I/O读和写周期 与M的不同点 1.基本I/O操作是T1、T2、T3、TW、T4组成占5个时钟周期 2.A19-A16为0 3.T3后,插入一个TW状态 4.读写IORC AIOWC

第五章 半导体存储器 第一节 半导体在存储器的分类 功能上分为: RAM 存放、写入、存放、输入出数据、中间结果。 ROM 只能读出、存放固定的程序 结构分为: 内存:速度快,容量小 外存:程序集成度低 RAM: 双级型 速度快 6管触发器 MOS :静态SRAM 动态DRAM ROM: 掩膜ROM PROM EPROM 第二节 RAM读写存储器 一、基本存储电路 1)无管静态存储电路

写入:X、Y输入高电平 T5、T6、T7、T8导通 读出:某电路的信号被选中 T5、T6导通,A与D0、B与D0且T7与T8导通,且T7、T8导通。 存储电路的信号被送至I/O与I/O线上。 由其电流方向即可判定存储单元的信息“1”还是“0”也可只有一个输出端接到外部,以有无电流通过D判定存储信息。 信息:非破坏性(信息读出后,仍保留在存储电路内) 2)单管存储电路(动态RAM) 由T1和电容C构成 写选择线位“1”T1选通 写入信号由位线(数据线)存入C 读出:选择线为“1”、C的电荷 通过T1输出到数据线上,通过放大器得到存储信息 (破坏性的,不保留信息)

二、RAM的结构 一个基本存储器电路表示一个二进制位,存储电路有规则地组合起来,就是存储器。用不同的地址信号表示不同的存储单元。 地址寄存器 选择所需要的单元存储器 地址译码器 (一)存储体 (二)外围电路 、地址译码器:内存64K,地址信息位16位(2的16次方为64K)。CPU要选择某一单元就在地址线总线输出此单元。地址信息给存储器,经过译码,选择需要访问单元。 、I/O电路:处于数据总线和被选单元之间,用以控制被选中的单元的读出或写入,并具有放大作用。 、片选控制CS端:一个存储体总由一定数量的RAM片组成在地址选择时,首先要选片,用地址译码器和控制信号构成,只有选中某一片时,此片所连的地址线才有效。

4、集电极开路或三态输出缓冲器 为扩展存储器的字段,常把几片RAM的数据线并联使用或与数据线相解,用此电路。 三态输出电路:两个或非门和两个NMOS(T1、T2)及一个非门 在RAM中设置三态输出缓冲器,使数据的输出受读写信号控制,另外还受CS 控制,从而可使多片RAM的数据输出线并联到数据总线上。 (三)地址译码的方式 地址译码: 1)字结构(单译码) 2)符合译码(双译码) 1.单译码

2.双译码 n位输入端译码器分成两个 若n=10,输出状态2的10次方=1K,译码线为2×2的5次方=64根 32×32的矩阵需要10根地址线A0~A9 A0~A4――X译码器2的5次方 1-32行 A5~A9――Y译码器2的5次方 1-32列 若输入地址为00,0000,0000 A0~A5 00000 选中第一行 X1=1 A5~A9 00000 选中第一列 Y1=1 其中存储器采用6管静态存储电路 A0~A4 00000 选中 1-1, 1-2……1-32 A5~A9 00000 选中 1-1, ……….32-1 双向译码 X方向控制32个电路,需要驱动器 intel2114是1K×4位 1K字――地址线位A0~A9 行――A3~A8 6根→64根 行选择线 列――A0、A1、A2、A9 4根→16根 列选择线 M的内部数据通过I/O电路、输入、输出的三态门与数据总线相连,由CS写允许信号一起控制这些三态门。

Intel2114 静态RAM 1K×4位 内部数据通过I/O输入、输出的三态门与数据线相连 由CS、WE控制三态门 WE=0 输入三态门导通、信号经数据总线写入M WE=1 输出三态门导通、信号经存储器读到数据总线 三、RAM与CPU的连接 连接包括: 1、地址线的连接 2、数据线的连接 3、控制器的连接 考虑方向 1.CPU总线的负载能力(小型:直接相连接;大型:加缓冲的驱动) 2.CPU时序和存储器的存取速度之间的配合 3.存储器的地址分配和选片 内存: RAM : 系统区 用户区(数据区、程序区) ROM 考虑存储器的容量有限,许多 片组成

4.控制信号的连接 CPU M I/OM, RD, WR WAIT 举例: (一)1KRAM的连接 1、4、8位存储器的结构 1K位存储器总结 1024×1、256×4 因此与八位CPU相连可采用联位并联或地址串连的方法来满足存储器需要的容量和位数。 若组成1K×8位,采用1024×1位、256×4的片子