Comprehensive Overview of Single and Multicycle Datapath for MIPS Architecture

This document provides an in-depth exploration of the single cycle and multicycle datapath architectures used in MIPS (Microprocessor without Interlocked Pipeline Stages). It covers the fundamental operations of instruction fetching, decoding, execution, and memory access, along with exception and interrupt handling. Additionally, it elucidates the specific roles of components such as ALU, registers, control logic, and multiplexers in processing various instruction types, ensuring a solid understanding of the MIPS architecture's functionality and efficiency.

Comprehensive Overview of Single and Multicycle Datapath for MIPS Architecture

E N D

Presentation Transcript

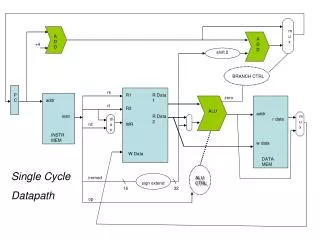

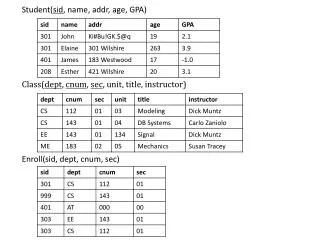

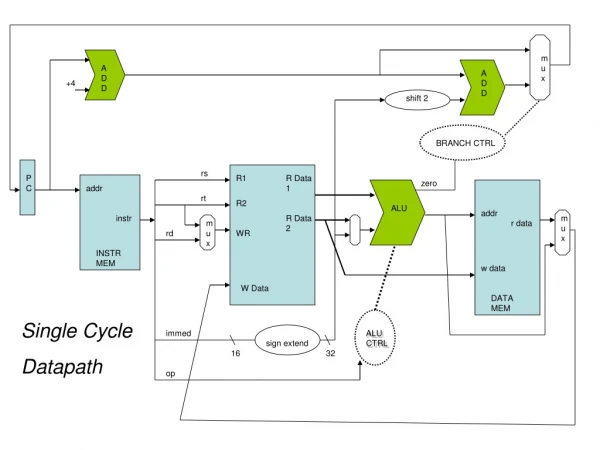

mux ADD ADD +4 shift 2 BRANCH CTRL rs PC R1 R Data 1 zero addr rt R2 ALU addr instr R Data 2 mux mux r data rd WR INSTR MEM w data W Data DATA MEM Single Cycle Datapath immed ALU CTRL sign extend 16 32 op

Multicycle Datapath jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data MR fetch decode execute (1..3) REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

Multicycle with Exception/Interrupt Handling jump addr shift 2 handler addr zero rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data overflow rd MEMORY PC - 4 W Data MR EPC to? REGISTERS immed sign extend shift 2 CAUSE 00 01 10 11 op fctn shamt CONTROL to?

Pipelined Datapath +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend IF ID EX MEM WB

add rd, rt, rs: Fetch +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data Instruction Fetch: Load IR, PC = PC + 4 w data Data Memory sign extend IF Register Contains IR and PC, and other values

add rd, rt, rs: Decode +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend ID register contains A, B, and other values Instruction Decode: Load data1, data2 into A, B (part of ID)

add rd, rt, rs: Execute +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Execute: sum of A, B into ALUout (part of EX)

add rd, rt, rs: MEM +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend MEM: (no memory access) save ALU result in MEM

add rd, rt, rs: WB +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Write Back: write sum to register rd

sw rt, offset(rs): Fetch +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend

sw rt, offset(rs): Decode +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend ID gets rs, rt, and immed+sign ext

sw rt, offset(rs): Execute +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend EX gets rs+offset, and rt

sw rt, offset(rs): MEM +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Write Data Memory [address] with rt value; nothing of interest in WD Data Memory sign extend

sw rt, offset(rs): WB +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory Registers not written in this instruction sign extend

A program fragment with 6 instructions 1. add r1, r2, r3 2. sw r4, 2232 ( r5 ) 3. addi r6, 55 4. lw r7, 1001 (r8) 5. bneq r7, r6, -3 6. add r1, r7, r0

A program fragment with 6 instructions 1. add r1, r2, r3 2. sw r4, 2232 ( r5 ) 3. addi r6, 55 4. lw r7, 1001 (r8) 5. slti r7, r6, -3 6. add r1, r7, r0

Six instructions 1,2,3,4,5,6: Step 1 +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Fetch 1

Six instructions 1,2,3,4,5,6: Step 2 +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Fetch 2 Decode 1

Six instructions 1,2,3,4,5,6: Step 3 +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Fetch 3 Execute 1 Decode 2

Six instructions 1,2,3,4,5,6: Step 4 +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Decode 3 Execute 2 Mem 1 Fetch 4

Six instructions 1,2,3,4,5,6: Step 5 +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Fetch 5 Decode 4 Execute 3 Mem 2 (sw) WB 1 (add)

Six instructions 1,2,3,4,5,6: Step 6 +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Execute 4 Mem 3 (addi) Fetch 6 Decode 5 WB 2 (sw: no write)

Six instructions 1,2,3,4,5,6: Step 7 +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Mem 4 (lw) Execute 5 Decode6 WB 3 (addi)

Six instructions 1,2,3,4,5,6: Step 8 +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Mem 5 (slti) Execute 6 WB 4 (lw)

Six instructions 1,2,3,4,5,6: Step 9 +4 add add Registers shift mux addr read1 PC read2 data1 out write ALU mux addr mux data2 r data Instruction Memory w data w data Data Memory sign extend Mem 6 (add) WB 5 (slti)

jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data add rd, rs, rt fetch: load ir, pc=pc+4 decode execute MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

Multicycle Datapath jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data MR fetch decode execute REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data add rd, rs, rt fetch decode:load A,B registers execute MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data add rd, rs, rt fetch decode execute (2 cycles) load alu out; load register MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data bne rs, rt, addr fetch: load IR, pc=pc+4 decode execute MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd bne rs, rt, addr fetch decode: load A B, aluout = immediate (extendx2)+pc execute MEMORY W Data MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd bne rs, rt, addr fetch: decode: execute: (1 cycle) compare A, B (holding rs, rt); if neq, load pc with aluout (holding branch addr) MEMORY W Data MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data lw rt, offset ( rs) fetch: load IR, pc=pc+4 decode execute MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data lw rt, offset ( rs) fetch decode: load A B; offset is ready execute MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data lw rt, offset ( rs) fetch decode execute: (3 cycles): load aluout with addr, load mr with data, load register rt MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

Multicycle Datapath jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data Try these: sw rt, off(rs) j addr andi rd,rs,rt MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

Multicycle Datapath z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data MR REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL

R-Format: add, slt, sll rs PC R1 R Data 1 addr rt R2 ALU instr R Data 2 WR rd INSTR MEM DATA MEM W Data fctn ALU CTRL op shamt

mux ADD ADD +4 shift 2 BRANCH CTRL rs PC R1 R Data 1 zero addr rt R2 ALU instr R Data 2 WR INSTR MEM DATA MEM W Data immed ALU CTRL sign extend 16 32 op I-Format bne

I-Format lw, sw rs PC R1 R Data 1 zero addr rt R2 ALU addr instr R Data 2 R Data mux WR INSTR MEM W Data W Data DATA MEM immed ALU CTRL sign extend 16 32 op

mux ADD ADD +4 shift 2 BRANCH CTRL address PC R1 R Data 1 zero addr R2 ALU instr R Data 2 WR INSTR MEM DATA MEM W Data ALU CTRL op J-Format

Multicycle Datapath jump addr shift 2 z rs addr R1 R Data 1 A PC rt ALU alu out R2 IR data R Data 2 B +4 WR w data rd MEMORY W Data MR fetch decode execute REGISTERS immed sign extend shift 2 op fctn shamt ALU CTRL