Computer Arithmetic Lecture 10: MIPS Divide Instruction

This lecture covers the MIPS divide instruction and various division algorithms. It delves into paper-and-pencil division methods, hardware implementations for division, and refinements in divide algorithms. Observations on different versions of divide algorithms are discussed, focusing on improving efficiency and operation. The session also explores signed divides, overflow checks, and considerations for handling large integers in division operations. Furthermore, it reviews MIPS instructions and the ISA, including floating-point representation for numbers in computer systems.

Computer Arithmetic Lecture 10: MIPS Divide Instruction

E N D

Presentation Transcript

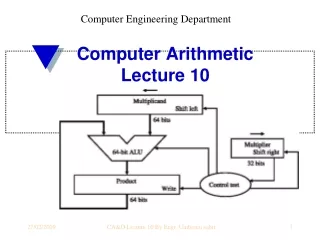

Computer Engineering Department Computer ArithmeticLecture 10 CA&O Lecture 10 By Engr. Umbreen sabir

000000 $s2 $s3 00000 00000 27 000000 $s2 $s3 00000 00000 26 op rs rt rd shamt funct MIPS Divide Instruction • div $s2, $s3 • The division quotient is placed in processor dedicated register lo and the remainder is placed in processor registerhi • div uses signed integers and result is a signed 64-bit number. Overflow and division by 0 are checked in software • MIPS uses divu for unsigned divisions CA&O Lecture 10 By Engr. Umbreen sabir

Division: Paper & Pencil 1001tenQuotient 10 101 1010–1000 –1000 Divisor1000ten 1001010tenDividend 10 Remainder (or Modulo result) A number can be subtracted, creating quotient bit on each step • Binary => 1 * divisor or 0 * divisor Dividend = Quotient x Divisor + Remainder=> | Dividend | = | Quotient | + | Divisor | We assume for now unsigned 32-bit integers. 3 versions of divide, successive refinement CA&O Lecture 10 By Engr. Umbreen sabir

Initially holds divisor Initially holds 0s If Reminder63 = 1, Quotient0=0 Reminder63 = 0, Quotient0=1 Initially holds dividend Division Hardware (Version 1) • 64-bit Divisor register, 64-bit ALU, 64-bit Remainder register, 32-bit Quotient register CA&O Lecture 10 By Engr. Umbreen sabir

Divide Algorithm Version 1 CA&O Lecture 10 By Engr. Umbreen sabir

Observations on Divide Version 1 • 1/2 bits in divisor always 0=> 1/2 of 64-bit adder is wasted => 1/2 of divisor is wasted • Instead of shifting divisor to right, shift the remainder to left? • 1st step cannot produce a 1 in quotient bit (otherwise too big for the register) => switch order to shift first and then subtract, can save 1 iteration CA&O Lecture 10 By Engr. Umbreen sabir

If Reminder63 = 1, Quotient0=0 Reminder63 = 0, Quotient0=1 Division Hardware (Version 2) • 32-bit Divisor register, 32-bit ALU, 64-bit Remainder register, 32-bit Quotient register CA&O Lecture 10 By Engr. Umbreen sabir

Observations on Divide Version 2 • We can eliminate Quotient register by combining with Remainder as it is shifted left • Start by shifting the Remainder left as before. • Thereafter loop contains only two steps because the shifting of the Remainder register shifts both the remainder in the left half and the quotient in the right half • The consequence of combining the two registers together and the new order of the operations in the loop is that the remainder will be shifted left one time too many. • Thus the final correction step must shift back only the remainder in the left half of the register CA&O Lecture 10 By Engr. Umbreen sabir

At the end right half holds quotient At the start dividend is here Division Hardware (Version 3) • 32-bit Divisor reg, 32 -bit ALU, 64-bit Remainder reg, (0-bit Quotient reg) CA&O Lecture 10 By Engr. Umbreen sabir

Divide Algorithm Version 3 Divide 0000 0111 by 0010 (2s 1110) Iteration Divisor Remainder reg oper? 0. 00100000 0111 in. val 0a 0010 00001110 shft lf 1 1a 0010 1110 1110 Rem=Rem-Div 1b 0010 0000 1110 Rem=Rem+Div 0001 1100 sll Rem, R0=0 2a 0010 1111 1100 Rem=Rem-Div 2b 0010 0001 1100 Rem=Rem+Div 0011 1000 sll Rem, R0=0 3a 0010 0001 1000 Rem=Rem-Div 3b 0010 0011 0001 sll Rem, R0=1 4a 0010 0001 0001 Rem=Rem-Div 4b 0010 0010 0011 sll Rem, R0=1 Shift left half Of Rem right 1 0001 0011 CA&O Lecture 10 By Engr. Umbreen sabir

Observations on Divide Version 3 • Same Hardware as Multiply: just need ALU to add or subtract, and 64-bit register to shift left or shift right • Hi and Lo registers in MIPS combine to act as 64-bit register for multiply and divide • Signed Divides: Simplest is to remember signs, make positive, and complement quotient and remainder if necessary • Note: Dividend and Remainder must have same sign • Note: Quotient negated if Divisor sign & Dividend sign disagreee.g., –7 ÷ 2 = –3, remainder = –1 • And 7 ÷ (– 2)= – 3, remainder = 1 • Possible for quotient to be too large: if divide 64-bit integer by 1, quotient is 64 bits (“called saturation”) CA&O Lecture 10 By Engr. Umbreen sabir

Review: MIPS Instructions, so far CA&O Lecture 10 By Engr. Umbreen sabir

Review: MIPS ISA, continued CA&O Lecture 10 By Engr. Umbreen sabir

Review: MIPS ISA- continued CA&O Lecture 10 By Engr. Umbreen sabir

Floating-Point • What can be represented in N bits? • Unsigned 0 to 2N • 2s Complement - 2N-1 to 2N-1 - 1 • With MIPS singed integers the 32-bit architecture allows us to represent numbers in the range ±2.15Χ109 • But, what about very large numbers? 9,349,398,989,787,762,244,859,087,678 • What about very small numbers? 0.0000000000000000000000045691 • Floating point representation allows much larger range at the expense of accuracy CA&O Lecture 10 By Engr. Umbreen sabir

Normalized notation – single number to the left of decimal point (no leading 0s) Exponent - how many digits the decimal point is moved to left to get to 1 Sign, magnitude 23 yyyyyyy -24 1.02 x 10 -1.673 x 10 ±1.xxxxx….. 2 radix (base 2) radix (base) significand Number of xs determines accuracy Sign, magnitude Number of ys determines range Scientific Notation Decimal notation Binary notation (binary floating point) CA&O Lecture 10 By Engr. Umbreen sabir

1 8 bits 23 bits S E sign M mantissa: sign + magnitude, normalized binary significand Signed exponent 1 11 bits 20 bits S E sign M Signed exponent M 32 bits MIPS Register bit allocation • Representation of floating point means that the binary point “floats” - to get a non-0 bit before it. The binary point is not fixed. • Since number of bits in register is fixed - we need tocompromise • When exponent is too large – or too small – an exception Overflow, or underflow • Representation of 2.0tenx10-38 to 2.0tenx1038. In double-precision two registers are used. This increases the range to 2.0ten x10-308 to 2.0tenx10308.Significand now has 52 bits. CA&O Lecture 10 By Engr. Umbreen sabir

S E-127 N = (-1) 2 (1.M) IEEE 754 Floating Point Standard • Representation of floating point numbers in IEEE 754 standard - assures uniformity across computer implementations. • The 1 in significand is implicit - 0ten is given as a reserved representation 00…..000two • The rest of the numbers are • Placing the sign bit and exponent first makes easier integer comparisons for sorting • Using an exponent bias allows exponent to be unsigned, smallest being 00…000two largest being 11…111two. Makes comparisons easier • Double precision bias is 1023ten.Underflow and overflow can still occur CA&O Lecture 10 By Engr. Umbreen sabir

S N = (-1)(1+s1•2-1+s2•2-2+ .. +s23•2-23)2(E-bias) 1 1000 0011 111000….. 0 (27+21+20-127) N = (-1) (1+2-1+2-2+2-3)2 (131-127) N = -1.875 2 IEEE 754 - continued • If the 23 significand bits are numbered from left-to-right then the floating point number represented by these bits is • So the register containing the bits represents N = -1.87524 = -1.875 16= -30 CA&O Lecture 10 By Engr. Umbreen sabir

23 bits sp 0 1000 0010 01000….. 0 20 bits dp 0 100 0000 0010 01000….. 0 32 bits 0 0000 00 00000….. 0 Exercise • Show the IEEE 754 representation of 10ten in single and double precision 10ten = 1010two = 1.01 23 in normalized notation • The sign bit is 0, the exponent is 3+127 = 130= 1000 0010two • In double precision the exponent is3+1023= 1026 = 100 0000 0010two CA&O Lecture 10 By Engr. Umbreen sabir