D-FlipFlop Operation Simulation with VHDL Process Synchronization

This document outlines a VHDL simulation of a D-FlipFlop's operation using a synchronized process. The simulation initiates on a low clock signal and executes logical operations to determine output values based on input signals. The process is designed to automatically restart without the need for manual looping, ensuring consistent behavior across simulations. It encompasses entity declarations, architecture setups, signal generation, and process monitoring to efficiently display the functionality of the D-FlipFlop in response to varying input signals over time.

D-FlipFlop Operation Simulation with VHDL Process Synchronization

E N D

Presentation Transcript

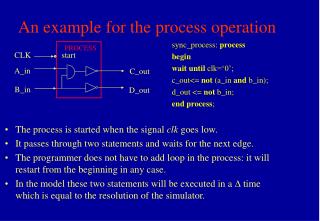

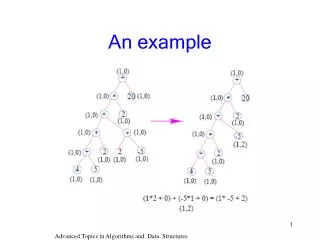

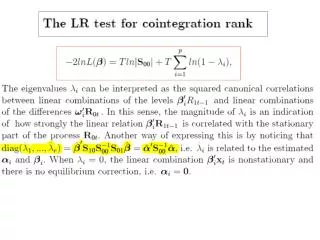

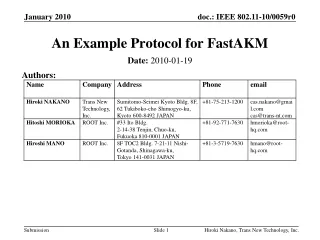

PROCESS CLK start A_in C_out B_in D_out An example for the process operation sync_process: process begin wait until clk=‘0’; c_out<= not (a_in and b_in); d_out <= not b_in; end process; • The process is started when the signal clk goes low. • It passes through two statements and waits for the next edge. • The programmer does not have to add loop in the process: it will restart from the beginning in any case. • In the model these two statements will be executed in a time which is equal to the resolution of the simulator.

ENTITY cir IS PORT (A_in,B_in,clk: IN BIT; c_out,D_out: OUT BIT); END cir; ARCHITECTURE bhv OF cir IS -- This is the declaration part of the architecture BEGIN -- This is the body of the architecture sync_process:process -- This is a comment, this is the declaration part -- of the process begin wait until clk='0'; c_out<= not (a_in and b_in); D_out <= not b_in; end process; end bhv;

ENTITY stm IS PORT (A_in,B_in,clk: out BIT; c_out,d_out: in BIT); END stm; ARCHITECTURE dtf OF stm IS BEGIN A_in <= '1' AFTER 0 ns, '1' AFTER 10 ns, '0' AFTER 20 ns, '1' AFTER 55 ns; B_in <= '0' AFTER 0 ns, '1' AFTER 10 ns, '0' AFTER 20 ns, '0' AFTER 55 ns;

clk <= '0' AFTER 0 ns, '1' AFTER 10 ns, '0' AFTER 20 ns, '1' AFTER 30 ns, '0' AFTER 40 ns, '1' AFTER 50 ns, '0' AFTER 60 ns, '1' AFTER 70 ns, '0' AFTER 80 ns, '1' AFTER 90 ns; END dtf;

ENTITY stm IS PORT (A_in,B_in,clk: out BIT; c_out,d_out: in BIT); END stm; ARCHITECTURE dtf OF stm IS signal clk_A_B: bit_vector(0 to 2); BEGIN clk_A_B <= "010" after 0 ns, "101" after 10 ns, "010" after 20 ns, "100" after 30 ns, "000" after 40 ns, "110" after 50 ns, "001" after 55 ns,

"001" after 60 ns, "111" after 70 ns, "011" after 80 ns, "101" after 90 ns; clk <= clk_A_B(0); A_in <= clk_A_B(1); B_in <=CLK_A_B(2); END dtf;

ENTITY bnc IS END bnc; use std.textio.all; ARCHITECTURE str OF bnc IS COMPONENT cir PORT (A_in,B_in,clk: IN BIT; c_out,d_out: OUT BIT); END COMPONENT; COMPONENT stm PORT (A_in,B_in,clk: out BIT; c_out,d_out: in BIT); END COMPONENT; SIGNAL wA_in,wB_in,wclk,wC_out,wD_out: BIT; for all: cir use entity work.cir (bhv); for all: stm use entity work.stm (dtf); -- Signals for the right order of the executions of the processes signal s,z:Boolean:=False; BEGIN circuit: cir PORT MAP(wA_in,wB_in,wclk,wC_out,wD_out); generator: stm PORT MAP(wA_in,wB_in,wclk,wC_out,wD_out);

-- Header of the results header: process variable dline1: line; variable dline2: line; constant L1: string:="This is the operation of the D-FlipFlop"; constant L2: string:=" TIME clk A_in B_in C_out D_out"; begin write (dline1, L1, right, 1); writeline (output, dline1); write (dline2, L2, right, 1); writeline (output, dline2); s<=True; wait; end process;

-- Monitoring the result and printing them out monitor: process (wA_in,wB_in,wclk,wC_out,wD_out) variable dline: line; begin if s=True and z=True then write (dline, NOW, right, 7); write (dline, wclk, right, 5); write (dline, wA_in, right, 6); write (dline, wB_in, right, 8); write (dline, wC_out, right, 10); write (dline, wD_out, right, 8); writeline (output, dline); end if; end process;

-- This is a line, only Underline: process variable dline: line; constant L: string:="=============================================="; begin wait on s; write (dline, L, right, 1); writeline (output, dline); z<=True; end process; END str;